# DESIGN OF A RESONANT SOFT SWITCHING POWER SUPPLY FOR STABILIZED DC IMPULSE DELIVERY

by

Andrew H. Seltzman

A thesis submitted in partial fulfillment of the requirements for the degree of

Master of Science

(Electrical Engineering)

at the

UNIVERSITY OF WISCONSIN-MADISON

2012

## **APPROVED**

Adviser Signature: \_\_\_\_\_\_\_\_

Adviser Title: \_\_\_\_\_\_\_

## **Abstract**

This thesis addresses the issues involved in the design and construction of a multiphase resonant switching power supply for delivery of a high voltage, high current stabilized DC impulse. Such a power supply may be used in place a pulse forming network (PFN) to drive a high power klystron amplifier, which typically requires voltages near -100kV at 10s of amps of current. Unlike an LC PFN, a switchmode power supply (SMPS) allows greater control over pulse duration while still allowing generation of longer duration pulses on the order of 10ms with constant output voltage by use of feedback regulation.

Specifically, the thesis documents the results from the design of a loosely coupled boost transformer with a parallel LC resonator on the secondary, a microcontroller based control system for feedback stabilization and techniques of harmonic mitigation to reduce switching noise on the output waveform.

# Acknowledgements

I would like to thank Giri Venkataramanan, Paul Nonn, Bob Ganch, Jason Kauffold and Jay Anderson for assisting with this project. I would also like to thank the UW Madison Department of Physics, and Los Alamos National Lab (LANL) for providing support for this research.

# Table of Contents

| Abstract    | i                                     |

|-------------|---------------------------------------|

| Acknowled   | dgements iii                          |

| Table of C  | Contentsiv                            |

| List of Fig | uresix                                |

| List of Tal | olesxiv                               |

| Nomencla    | turexv                                |

| Introducti  | on                                    |

| 0.1         | Overview1                             |

| 0.2         | Research Contributions                |

| 0.3         | Overview of Chapters4                 |

| Chapter 1   | State of the Art Review6              |

| 1.1         | High power SMPS Design and Topologies |

| 1.2         | Loosely Coupled Transformers          |

| 1.3         | Resonant SMPS Power Converters        |

| 1.4       | Harmonic Mitigation                           | 20 |

|-----------|-----------------------------------------------|----|

| 1.5       | Summary                                       | 22 |

|           |                                               |    |

| Chapter 2 | Power Supply Design Overview                  | 23 |

| 2.1       | Design Requirements and Constraints           | 24 |

| 2.2       | Summary                                       | 26 |

|           |                                               |    |

| Chapter 3 | Power Supply Design                           | 27 |

| 3.1       | Overview and Block Diagram                    | 29 |

| 3.2       | Capacitor Charging Power Supply               | 31 |

| 3.3       | Testing Capacitor Bank                        | 33 |

| 3.4       | Long Pulse Capacitor Bank                     | 35 |

|           | 3.4.1 Electrolytic Capacitors                 | 36 |

|           | 3.4.2 Capacitor Fuses                         | 36 |

|           | 3.4.3 Capacitor Bank Bus Plates               | 37 |

|           | 3.4.4 Capacitor Bank Interconnect Cables      | 38 |

| 3.5       | Switching Network Design                      | 39 |

|           | 3.5.1 Topology                                | 39 |

|           | 3.5.2 Cable Interconnects From Capacitor Bank | 40 |

|           | 3.5.3 Low ESL Stiffening Capacitor Bank       | 41 |

|           | 3.5.4 Low Inductance Relay                    | 42 |

|           | 3.5.5 Low Inductance IGBT Busbars             | 43 |

|      | 3.3.6  | IGB1s and Gate Drivers                                   | 40 |

|------|--------|----------------------------------------------------------|----|

|      | 3.5.7  | Transformer Connections                                  | 47 |

| 3.6  | Transi | former Design                                            | 48 |

|      | 3.6.1  | Overview                                                 | 48 |

|      | 3.6.2  | Nano-crystalline Iron Core                               | 50 |

|      | 3.6.3  | Primary Winding                                          | 51 |

|      | 3.6.4  | Secondary Winding Enclosure                              | 52 |

|      | 3.6.5  | Secondary Winding                                        | 53 |

|      | 3.6.6  | Oil Tank Feedthroughs                                    | 54 |

|      | 3.6.7  | Parallel Resonator Capacitor                             | 57 |

|      | 3.6.8  | Variation of Frequency, Turns Ratio, and Load Resistance | 58 |

| 3.7  | Doubl  | ing 3 Phase Rectifier                                    | 67 |

|      | 3.7.1  | Rectifier Stack Design                                   | 67 |

|      | 3.7.2  | Doubling Configuration                                   | 68 |

| 3.8  | Harmo  | onic Mitigation                                          | 70 |

|      | 3.8.1  | Capacitive Loading                                       | 70 |

|      | 3.8.2  | Parallel LC Harmonic Filter for 6th Harmonic Mitigation  | 70 |

| 3.9  | Safety | Systems                                                  | 72 |

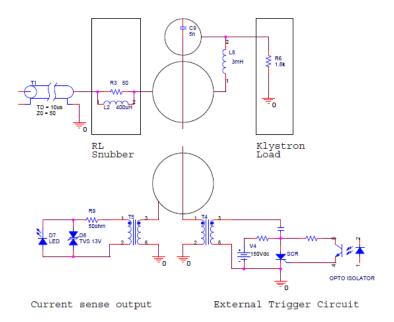

|      | 3.9.1  | LR Snubber                                               | 72 |

|      | 3.9.2  | Crowbar Spark Gap                                        | 73 |

| 3.10 | Summ   | nary                                                     | 76 |

| Chapter 4 | Control System Design                      |

|-----------|--------------------------------------------|

| 4.1       | Overview78                                 |

| 4.2       | dsPIC Microcontroller                      |

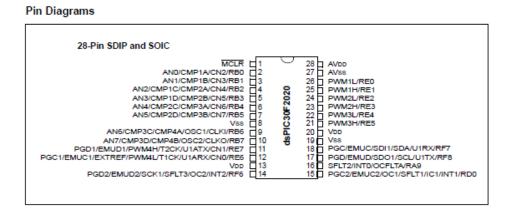

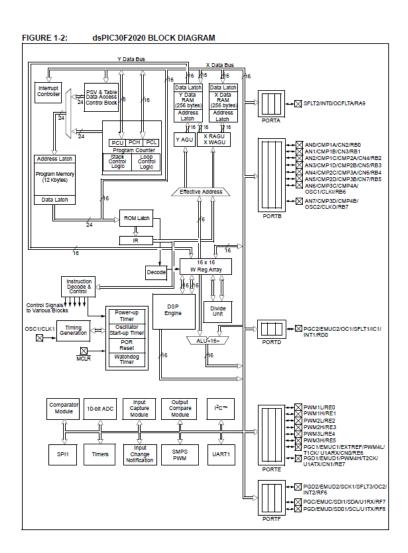

| 4.3       | Analog Input Galvanic Isolation82          |

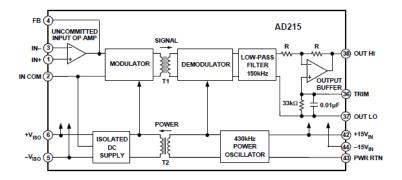

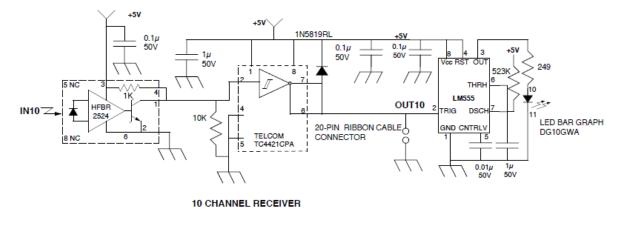

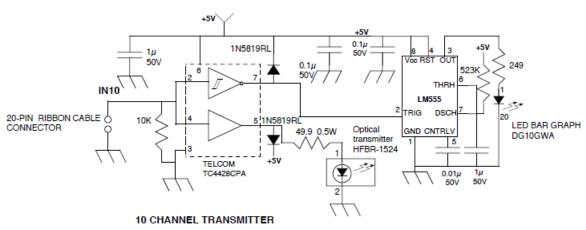

| 4.4       | Feedback Voltage Dividers                  |

| 4.5       | Current Measurement                        |

| 4.6       | Fiber Optic I/O                            |

| 4.7       | Microcontroller Code Design                |

| 4.8       | Summary 92                                 |

| Chapter 5 | Power Supply Testing93                     |

| 5.1       | Spice Simulation Model94                   |

| 5.2       | Open Loop Testing99                        |

| 5.3       | Feedback Controller Testing                |

| 5.4       | Filter Testing                             |

| 5.5       | Output Arc Fault Simulation and Testing113 |

| 5.6       | Summary                                    |

| Chapter 6 | Conclusions and Recommendations 119        |

| 6.1       | Summary of Research                        |

| 6.2       | Conclusions                                |

| 6.3      | Future Work                                                                |

|----------|----------------------------------------------------------------------------|

| Bibliogi | raphy125                                                                   |

| Append   | <i>ix</i> 1                                                                |

| A        | CM1200HB-66H IGBT                                                          |

| В        | Hipotronics 8XX Series Power Supplies                                      |

| C        | Matlab code for calculation voltage droop                                  |

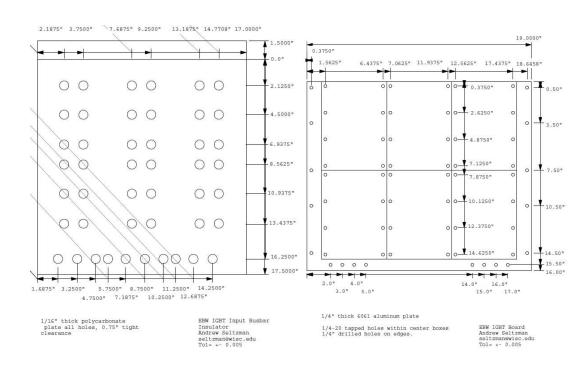

| D        | Low inductance relay CAD designs                                           |

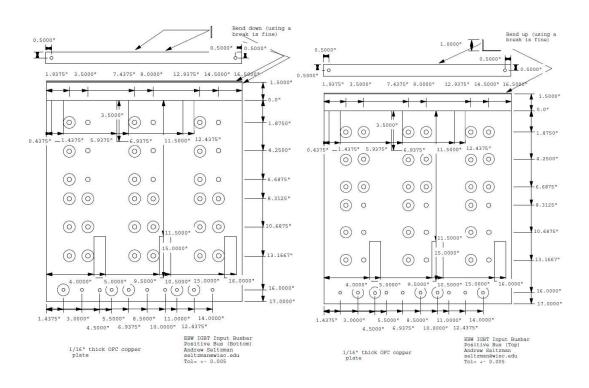

| Е        | IGBT busbar CAD designs                                                    |

| F        | CT concepts IGBT driver.                                                   |

| G        | Matlab code for resonant transformer plots                                 |

| Н        | Matlab code for plotting boost ratio at varying frequency                  |

| I        | Matlab code for date with differential voltage on transformer secondary 13 |

| J        | Matlab code for date with differential voltage on transformer primary 15   |

| K        | Pearson transformer datasheet. 17                                          |

| L        | AD215 datasheet                                                            |

| M        | Microcontroller datasheet                                                  |

| N        | Microcontroller operating code                                             |

# List of Figures

| Figure 1.1 Power supply output pulse without and with feedback control10 |

|--------------------------------------------------------------------------|

| Figure 1.2 Bipolar bank and IGBT h-bridge                                |

| Figure 1.3 Transformer primary waveform [4].                             |

| Figure 1.4 Three phase resonant transformer system.                      |

| Figure 1.5 Rectifier, doubler, filter and RL snubber.                    |

| Figure 1.6 Unipolar bank and IGBT h-bridge                               |

| Figure 1.7 Resonant primary tank circuit                                 |

| Figure 1.8 IGBT current and tank voltage[].                              |

| Figure 1.9 Output LC filter.                                             |

| Figure 3.1 Power Supply Block Diagram.                                   |

| Figure 3.2 Resonant power supply in construction                         |

| Figure 3.3 Hipotronics power supply                                      |

| Figure 3.4 Testing capacitor bank                                        |

| Figure 3.5 Testing bank voltage droop                                    |

| Figure 3.6 Main bank voltage droop                                       |

| Figure 3.7 Main bank capacitors                                          |

| Figure 3.8 Capacitor bank fuses                                          |

| Figure 3.9 Capacitor bank bus bars                                       |

| Figure 3.10 H-Bridge Topology.                                           |

| Figure 3.11 Capacitor bank interconnects.           | 40 |

|-----------------------------------------------------|----|

| Figure 3.12 Main capacitor bank interconnect block. | 41 |

| Figure 3.13 IGBT bypass capacitor connection.       | 42 |

| Figure 3.14 Low inductance relay.                   | 42 |

| Figure 3.15 IGBT output busbars.                    | 44 |

| Figure 3.16 Input busbars.                          | 44 |

| Figure 3.17 Busbar layer cross section.             | 45 |

| Figure 3.18 IGBT module connection flanges          | 46 |

| Figure 3.19 Mitsubishi CM1200HB-66H.                | 46 |

| Figure 3.20 Transformer connections.                | 47 |

| Figure 3.21 Resonant transformer configuration.     | 48 |

| Figure 3.22 Resonant transformer.                   | 49 |

| Figure 3.23 Resonant transformer design.            | 50 |

| Figure 3.24 Transformer core dimensions.            | 51 |

| Figure 3.25 Transformer primary.                    | 52 |

| Figure 3.26 Transformer primary dimensions.         | 52 |

| Figure 3.27 Oil tank dimensions                     | 53 |

| Figure 3.28 Transformer secondaries.                | 54 |

| Figure 3.29 Oil tank feedthroughs.                  | 54 |

| Figure 3.30 Assembled oil tank components           | 55 |

| Figure 3.31 Aluminum plug                           | 55 |

| Figure 3.32 Polycarbonate tubes and supports.       | 56 |

| Figure 3.33 Transformer support plate.              | 56 |

| Figure 3.34 Resonator capacitor assembly.           | 57 |

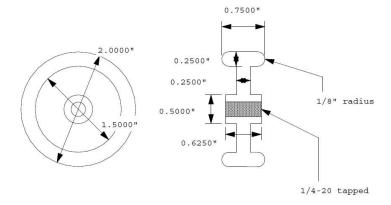

| Figure 3.35 Corona disk                                          | 58 |

|------------------------------------------------------------------|----|

| Figure 3.36 1.8kohm frequency responses.                         | 59 |

| Figure 3.37 820ohm frequency responses.                          | 59 |

| Figure 3.38 Leakage inductance models                            | 61 |

| Figure 3.39 Transformer model                                    | 61 |

| Figure 3.40 Simplified transformer model.                        | 62 |

| Figure 3.41 Spice simulation of simplified model                 | 63 |

| Figure 3.42 Comparison of transfer function and measured data    | 64 |

| Figure 3.43 Maximum boost ratio vs turns                         | 64 |

| Figure 3.44 Boost ratio at resonance for varying load resistance | 65 |

| Figure 3.45 Measured and calculated resonant frequency           | 66 |

| Figure 3.46 Doubling three phase rectifier.                      | 67 |

| Figure 3.47 Rectifier stack.                                     | 68 |

| Figure 3.48 Doubler capacitors                                   | 69 |

| Figure 3.49 LC harmonic filter.                                  | 71 |

| Figure 3.50 LR snubber.                                          | 73 |

| Figure 3.51 Spark gap schematic                                  | 74 |

| Figure 3.52 Spark gap.                                           | 75 |

| Figure 4.1 Control system                                        | 78 |

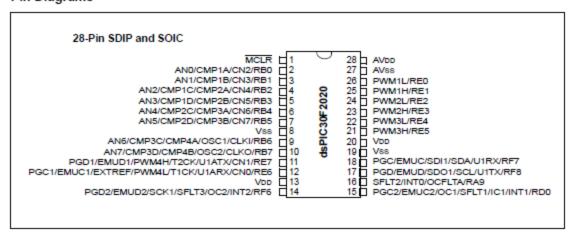

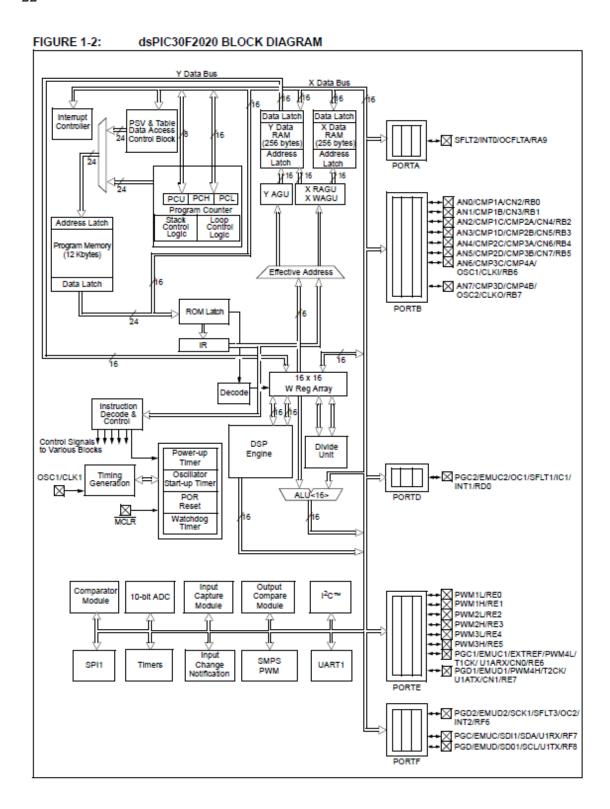

| Figure 4.2 dsPIC30F2020 pinout.                                  | 79 |

| Figure 4.3 Microcontroller subsystem block diagram               | 81 |

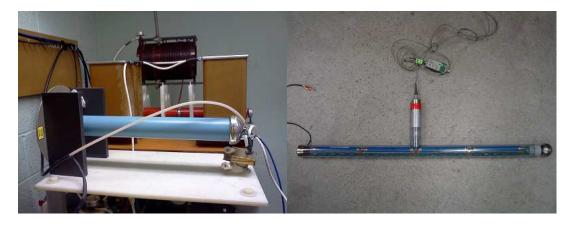

| Figure 4.4 Isolation modules.                                    | 82 |

| Figure 4.5 Isolator block diagram                                | 83 |

| Figure 4.6 High voltage probes                                   | 84 |

| Figure 4.7 Pearson transformer.                                          | 85  |

|--------------------------------------------------------------------------|-----|

| Figure 4.8 Fiber optic isolator                                          | 86  |

| Figure 4.9 Fiber optic interface                                         | 87  |

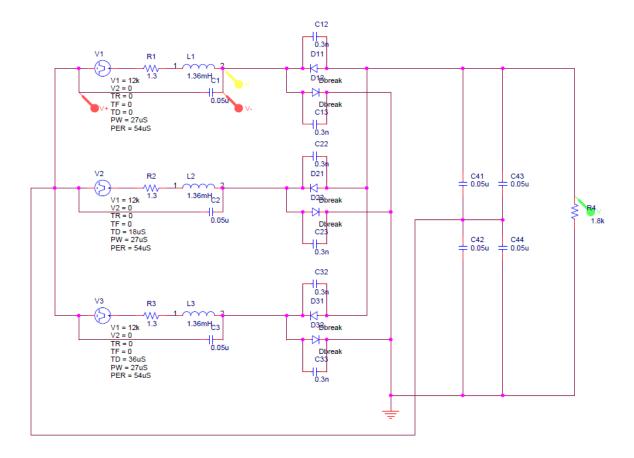

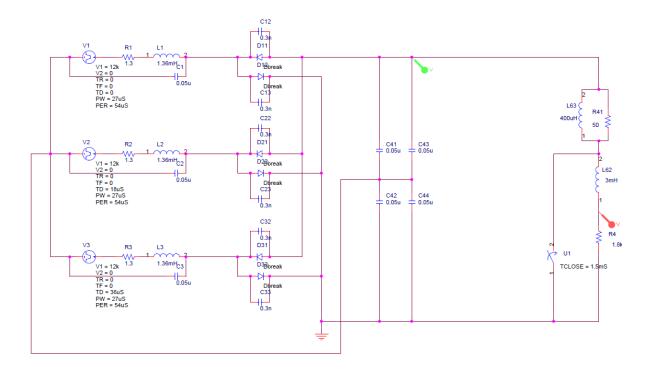

| Figure 5.1 Simplified spice model.                                       | 94  |

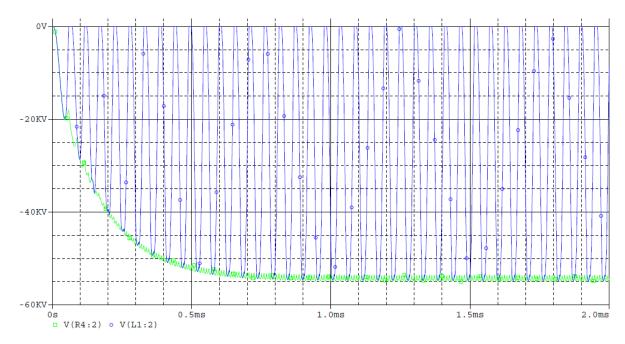

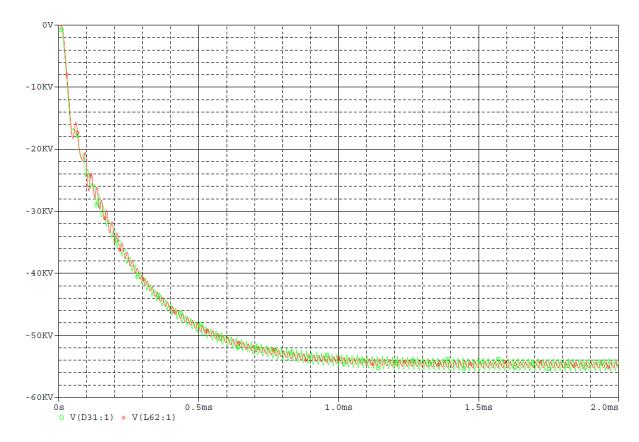

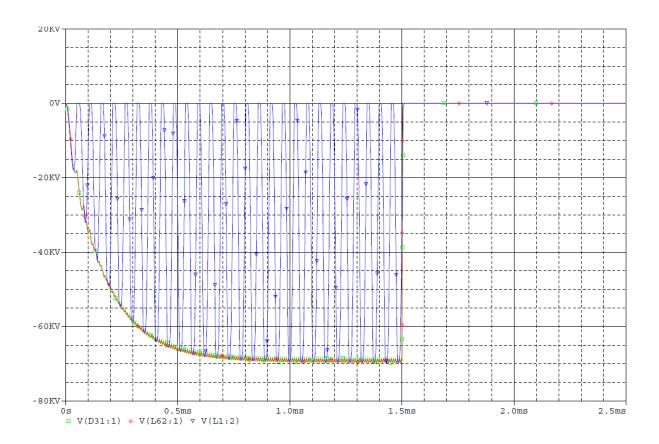

| Figure 5.2 Time domain simulation of output voltage.                     | 95  |

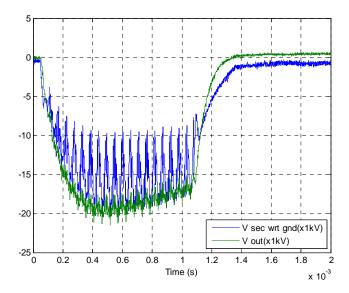

| Figure 5.3 Output voltage and phase voltage before median filter         | 96  |

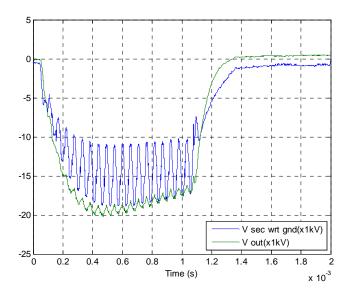

| Figure 5.4 Output voltage and phase voltage after 50 point median filter | 96  |

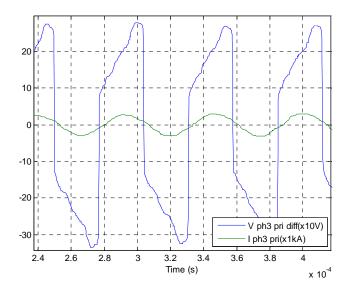

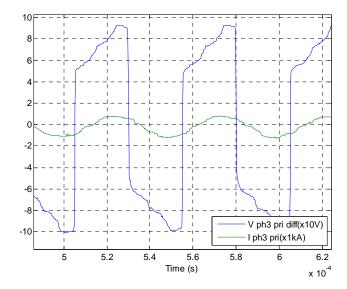

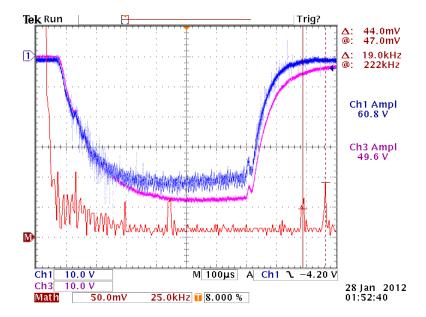

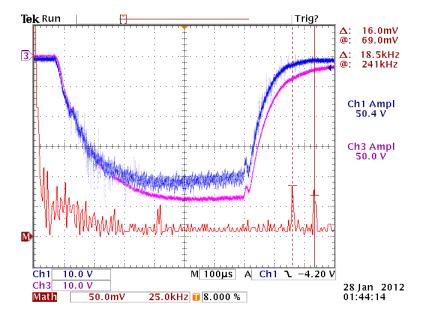

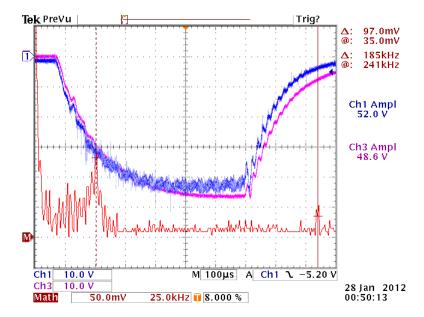

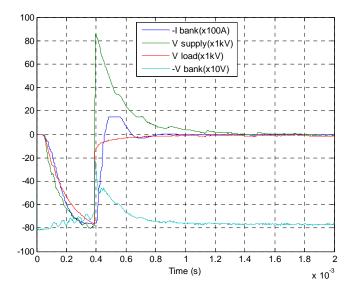

| Figure 5.5 Transformer primary voltage and current at 18.5kHz            | 97  |

| Figure 5.6 Transformer primary voltage and current at 19kHz              | 98  |

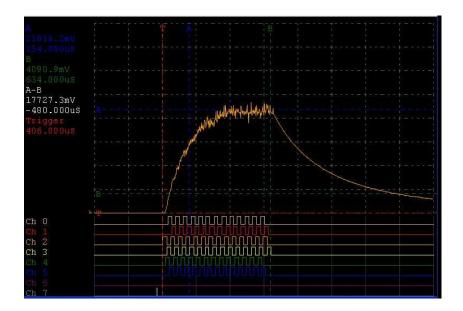

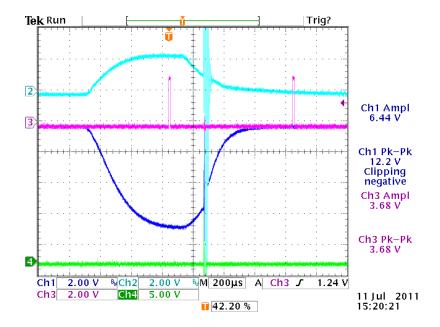

| Figure 5.7 Output voltage waveform and h-bridge gate drive signals       | 99  |

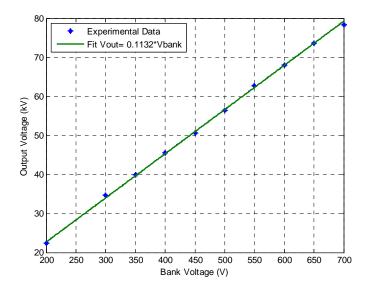

| Figure 5.8 Output voltage vs bank voltage at 20kHz operation             | 100 |

| Figure 5.9 Open loop pulse at 18.5kHz and 200V bank charge               | 101 |

| Figure 5.10 Open loop pulse at 20kHz and 200V bank charge                | 101 |

| Figure 5.11 Open loop pulse at 22kHz and 200V bank charge                | 102 |

| Figure 5.12 Open loop pulse at 24kHz and 200V bank charge                | 102 |

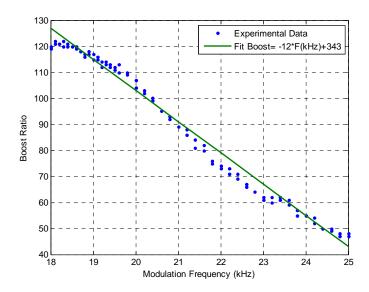

| Figure 5.13 Boost ratio vs switching frequency.                          | 103 |

| Figure 5.14 Microcontroller switching period vs required boost ratio     | 104 |

| Figure 5.15 Feed forward control stabilized output voltage.              | 105 |

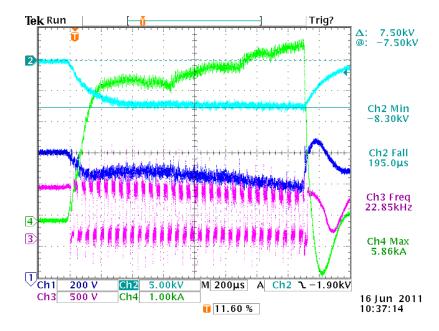

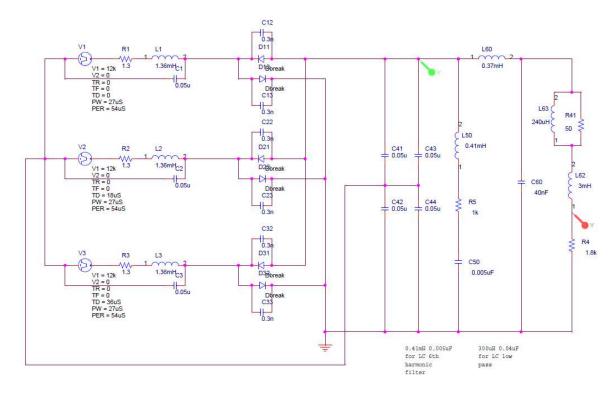

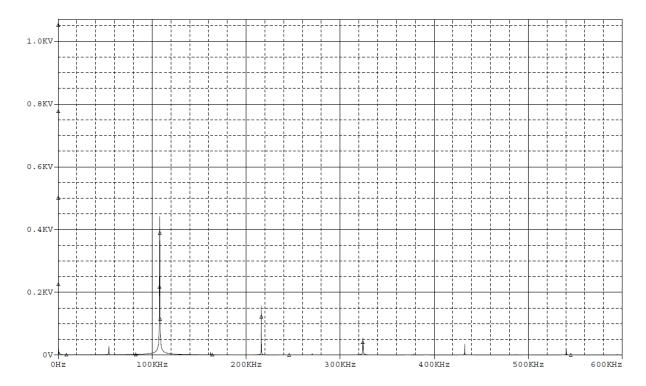

| Figure 5.16 Spice model with pi and harmonic filters                     | 106 |

| Figure 5.17 Spice time domain waveform with filters.                     | 107 |

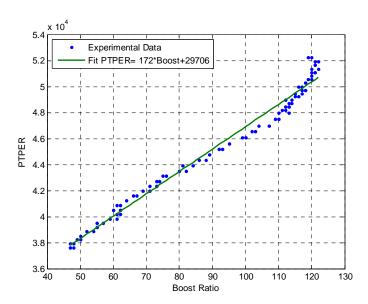

| Figure 5.18 Balanced three phase operation at 70kV.                      | 108 |

| Figure 5.19 Pi and 6th harmonic filter.                                  | 109 |

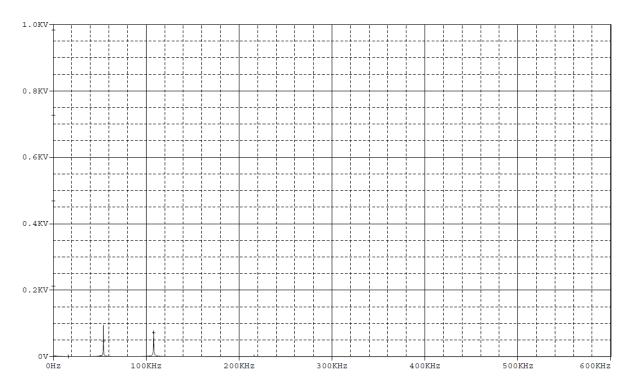

| Figure 5.20 Unbalanced three phase operation                             | 110 |

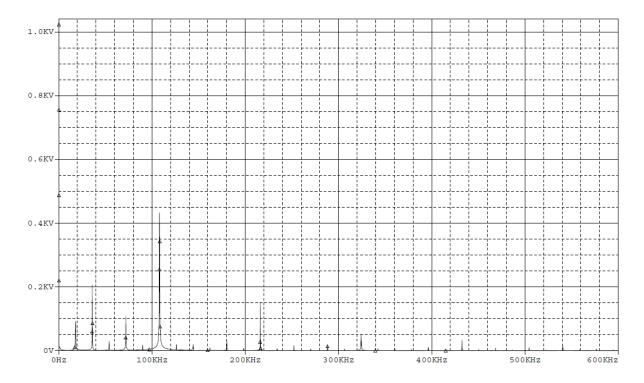

| Figure 5.21 Unfiltered operation.                                        | 111 |

| Figure 5.22 Operation with 6th harmonic filter.                             | .111 |

|-----------------------------------------------------------------------------|------|

| Figure 5.23 Operation with pi and 6th harmonic filters.                     | .112 |

| Figure 5.24 Spice model for spark gap simulation.                           | .113 |

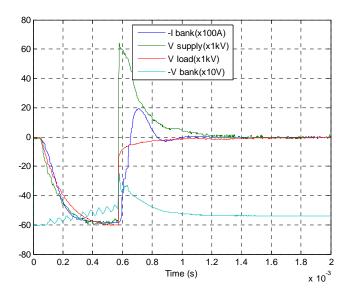

| Figure 5.25 Simulation of voltages during spark gap firing.                 | .114 |

| Figure 5.26 HV pulse caused by arc without snubber.                         | .115 |

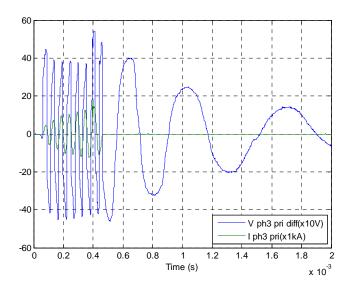

| Figure 5.27 Voltages during spark gap remote trigger                        | .116 |

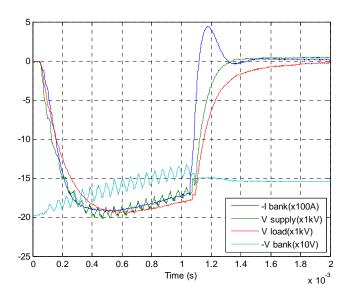

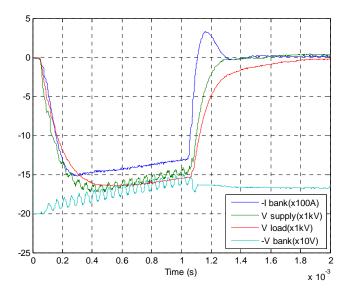

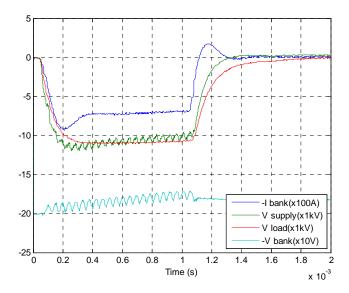

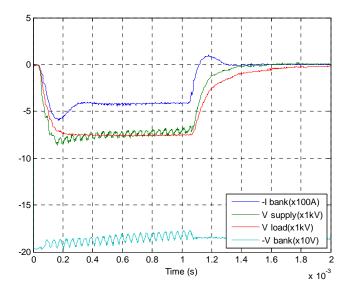

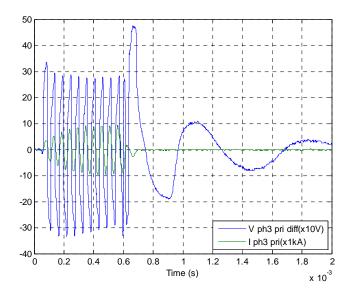

| Figure 5.28 Phase current and voltages during spark gap remote trigger      | .116 |

| Figure 5.29 Voltages during spark gap overvoltage trigger                   | .117 |

| Figure 5.30 Phase current and voltages during spark gap overvoltage trigger | .117 |

# List of Tables

| Table 1-1 Nano Material Characteristics [4]    | 11 |

|------------------------------------------------|----|

|                                                |    |

| Table 3-1 Transformer Core Characteristics [4] | 51 |

# Nomenclature

ADC Analog to Digital Converter

DSP Digital Signal Processing

ESL Effective Series Inductance

IGBT Insulated Gate Bipolar Transistor

IRQ Interrupt Request

ISR Interrupt Service Routine

MIPS Million Instructions Per Second

OFC Oxygen Free Copper

PFN Pulse Forming Network

PWM Pulse Width Modulation

SCR Silicon Controlled Rectifier

SMPS Switch Mode Power Supply

UART Universal Asynchronous Receiver and Transmitter

ZCS Zero Current Switching

ZVS Zero Voltage Switching

## Introduction

#### 0.1 Overview

The use of resonant circuits in high voltage switching power converters allows the voltage boost ratio of the transformer to exceed the turns ratio, allowing for more compact designs and reduction of copper usage in the secondary winding. Further, the boost ratio's strong dependence on switching frequency allows the power supply to regulate output voltage by shifting switching frequency. By switching at full duty cycle near resonance, the primary voltage and current will be in phase, allowing for zero current switching (ZCS), and almost complete elimination of switching losses. As switching frequency moves away from resonance, the IGBT current at the switching event increases from zero, however with only two switching events per cycle, switching losses are considerably lower than if PWM feedback were used for voltage control. Additional benefits of resonant topologies include the strong dependence of power transfer on a matched output load; in the event of a short circuit, the resonant circuit will be de-Qed and power transfer will automatically reduce without damage to the supply or load.

The power supply described herein is a resonant three phase pulsed power converter capable of a nominal output of -80kV at 40A for 10ms. The input dc link of the power supply is connected to an electrolytic capacitor bank with a nominal starting voltage of 900V and sufficient capacitance to drive the supply for 10ms. The capacitor bank is connected to the

input of an h-bridge module that drives the boost transformers. Each transformer primary is independently driven by a dedicated IGBT H-bridge circuit that is fiber optically coupled to a microcontroller based control system. The transformers are driven with a full duty cycle square wave of varying frequency between 18.5kHz and 26kHz and have microcrystalline iron cores for low loss while providing adequate volt-seconds. Each resonant transformer has a parallel LC resonant circuit on the secondary winding. The secondary windings are configured in a Y configuration and connected to a voltage doubling three phase rectifier, where the output of the rectifier feeds a center tapped capacitor bank with the center tap connected to the Y point of the transformer secondaries. The output of the rectifier is also connected to a harmonic filter tuned to the 6<sup>th</sup> harmonic of the average operating frequency to greatly reduce ripple on the power supply output. Additionally, an LC low pass filter may be connected in series with the output to further reduce ripple at the expense of a slightly increased rise time of the HV pulse.

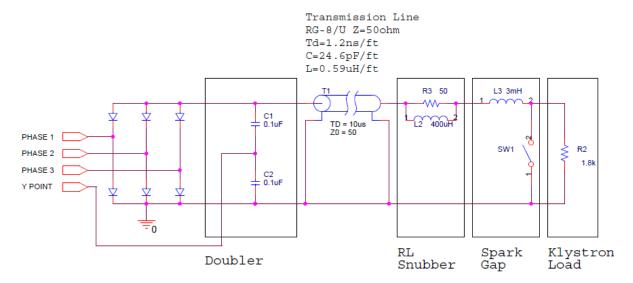

The power supply is connected to a klystron tube load with a nominal impedance of 1800ohm through an RG-8 solid dielectric coaxial cable. An RC snubber consisting of a 400uH inductor in parallel with a 50ohm resistor prevents an HV pulse from being reflected back up the coaxial cable in the event the output of the cable is shorted to ground by an internal HV arc. Additionally, a triggerable spark gap is placed in parallel with the klystron tube to crowbar the voltage across the cathode in the event of an internal arc in order to prevent arc damage to the cathodes emissive surface.

#### 0.2 Research Contributions

The main contributions of this research address the design and construction of a three phase resonant power supply. Specifically the contributions can be classified into the following groups:

- i. Design and analysis of a loosely coupled resonant transformer with a boost ratio that significantly exceeds the turns ratio with the capability of high voltage, high current output. The transformer in question includes a nano-crystalline iron core for low losses, and a specialized oil tank enclosing only the secondary winding for insulation and corona suppression.

- ii. Design of a suitable microprocessor based control system to generate switching signals to the IGBT module over a fiber optic link and receiving feedback signals from capacitor bank current, capacitor bank voltage, and output voltage. Maintaining good resistance to electromagnetic interference from high current switching events, and providing ground loop isolation to input signals. Providing computer control to adjust the output pulse parameters. Programing of a feedback control system to stabilize output voltage as the capacitor bank voltage decreases by adjusting switching frequency.

- iii. Mitigation of harmonic noise and ripple in the output through use of harmonic filters tuned to certain multiples of the switching frequency, inductive filers to make the output current stiff or low pass filters to selectively attenuate higher harmonics while still allowing rapid rise time at the beginning of the pulse.

iv. Design of a safety system for driving klystron tubes, that in the event of an internal arc, will cut output power from the supply, rapidly remove power from the load by use of a crowbar spark gap and prevent high voltage transients on the coaxial cable connecting the power supply to the load from being reflected back and damaging the supply.

#### 0.3 Overview of Chapters

Chapter one presents a review of state of the art designs of high power SMPS design, topologies, and soft switching. A review of existing high power resonant SMPS designs is presented along with results from their testing. Techniques for harmonic mitigation are reviewed.

Chapter two presents the requirements and design constraints for construction of the power supply. While later chapters describe the design of the power supply, this chapter provides insight into why the power supply was designed in this particular manner based on the components available. The power supply was constructed to replace an LC based PFN for delivering power to a microwave amplifier. Requirements on the power supply include output voltage and current capabilities, fault tolerance, output voltage range, output stability, pulse duration, serviceability, safety, tolerance for voltage droop on the capacitor bank, and external control of parameters. Design constraints include the use of certain transformer cores, IGBTs, rectifier diode stacks, and capacitor banks which were either donated to the project or were available as surplus.

Chapter three presents the design of the power supply's power electronic components, transformers, filtering system and safety systems. Components include the capacitor bank's

capacitor trays, bus bars and interconnecting wires, the IGBT switching network's mechanical relay, stiffening capacitors, low inductance bus plates, IGBTs, gate drivers and transformer connections, a detailed description of the resonant transformer, it's design, testing and comparison to numerical and analytical models, the three phase rectifier and it's doubling capacitor configuration, techniques of harmonic mitigation, and safety systems to prevent damage in the event of an arc fault.

Chapter four presents the design and construction of the power supplies control system. This chapter covers the microcontroller, its connecting circuits, i/o optical and galvanic isolators, and the design of the operating code.

Chapter five presents results from testing of the power supply and comparison to spice and analytical models. Models of the transformer, rectifiers, and filters are presented and compared to simulation. Open loop testing of the power supply is presented and compared to steady state spice simulations. Testing of the feedback control system and stabilization of output voltage during drooping capacitor bank in presented. Testing of the crowbar spark gam and associated LR snubber system is presented and compared to simulation.

Chapter six presents a brief summary of the research, presents conclusions and recommendations for resonant SMPS design, and outlines future research.

# Chapter 1 State of the Art Review

This chapter presents an overview of current research and development of pulsed power systems utilizing switched mode power supply (SMPS) systems for modulation and pulse stabilization. The first section presents several designs of high power SMPS, and high voltage SMPS topologies. The second section presents designs and characteristics of loosely coupled transformers. The third section covers resonant SMPS power converters, specifically a very similar design of a three phase resonant converter built at Los Alamos National Lab and results of its testing. The fourth section presents techniques of harmonic mitigation. The final section presents a summary of the chapter.

### 1.1 High power SMPS Design and Topologies

Design of high power SMPS converters is challenging due to the high voltages and currents involved. Power electronics must be capable of multi-megawatt power transfer, sometimes at thousands of volts and thousands of amps. The majority of high voltage power converters utilize either boost, flyback, or tightly or loosely coupled transformer based topologies. Boost and flyback converters are usually limited to low power operation, while tightly coupled high voltage systems may present safety hazards in the event of an output short due to the low impedance between the primary and secondaries of the transformer.

Poly-phase resonant power converters are a new method to generate high voltages with high power while maintaining a small physical size of 10 times smaller than previous methods. Such power converters are capable of producing 10s of MWs at 100s of kV. Additional benefits include inherent fault tolerance; the power converter must be designed to be matched to a given load such that in the event of a fault, the resonant circuit will be de-Qed thereby preventing power transfer. In the event of an arc fault, the system can safely run through the fault without damage to the load or supply, while the reduction in power transfer may be sufficient to clear the arc fault. Resonant power converters with amorphous nanocrystalline iron cores maintain the high permeability of iron cores, while allowing efficient use at higher frequencies in the 10s of kHz usually reserved for ferrite materials. Consequentially, a nano-crystalline transformer can provide 300 times the power transfer capability as a 60Hz transformer for a given size and weight [1]. For comparison, a 100kV, 60Hz system carrying 20Arms and utilizing soft iron cores will be on the scale of 35 tons and

have about 30kW losses while the transformer in a polyphase resonant converter operating at 140kV and 20kHz carrying 20Arms utilizing a nano-crystalline core will weight 450lbs and have about 3kW losses. Efficiency of as high as 97% may be realized with such a system. Such resonant systems can achieve significantly greater power levels with a given set power electronics in part to the resonant nature of the secondary which allows soft switching thereby reducing junction heating in the IGBTs. Given the exact nature of the system, either zero voltage switching or zero current switching may be utilized by switching the IGBTs during the period of reverse commutation of the anti-parallel diodes in the IGBT module, or by operating near resonance such that the IGBTs switch near the zero crossing period of primary current.

#### 1.2 Loosely Coupled Transformers

In contrast to closely coupled inductive systems, such as a tightly wound transformer with low leakage inductance, loosely coupled transformers provide a high leakage inductance that may be used to form a resonant circuit. In many cases efficient power transfer may only be attained if either or both the primary and secondary windings are capacitively compensated [2], described herein as a resonant transformer. In closely coupled reactive power systems, the reactive power is usually less than the real power transferred, while in certain loosely coupled systems, the reactive power can be up to 50 times the real power.

The majority of transformers used in the power supplies herein utilize a tightly wound uncompensated primary and a loosely coupled secondary with large leakage inductance and parallel capacitive compensation. Series compensation of the secondary leads to voltage source like characteristics while parallel compensation leads to current source like characteristics. Series compensation of the primary is utilized when the amplitude of the input waveform must be low, while parallel compensation is used when the primary winding must be concentrated into a small volume, thereby requiring high currents. The Q factor of a compensated winding is given by (1.1) as and is typically between 2 and 10.

$$Q = \frac{VAR}{P} \tag{1.1}$$

Larger secondary Q factors allow greater power transfer at the expense of a higher secondary VA utilization. The power transfer capability of a resonant transformer can be increased by increasing the VA rating of the secondary by adding more copper or core cross section, increasing the primary current or varying the coupling of the windings.

#### 1.3 Resonant SMPS Power Converters

Research in high power resonant power converters has been carried out at Los Alamos National Labs. The resonant power supply was designed to produce a high voltage pulse train of 140kV, at 1MW average, and 11MW peak that was used to drive klystron amplifiers. The output waveform was a chirp of 1.5ms pulses. The power supply drives the resonant transformers at a fixed 20kHz frequency using PWM to regulate the output waveform through feed forward and feedback techniques as shown in Figure 1.1 [3]. The supply used a resonant transformer with a nano-crystalline iron core and secondary LC resonator to achieve voltage boost to the required value. Zero voltage switching of the IGBTs was used to minimize switching losses.

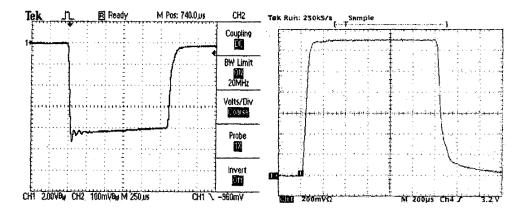

Figure 1.1 Power supply output pulse without and with feedback control.

The input DC link of the power converter used a bipolar capacitor bank charged to a nominal +/- 1250 V through a three phase SCR regulator connected to a 2100V substation. The capacitor bank utilized a series of custom low inductance metalized hazy polypropylene traction capacitors, designed to clear any internal short that may occur, thereby allowing

direct connection in parallel banks without individual capacitor safety fuses, which would increase inductance of the input DC link.

Each transformer was driven by an independent full h-bridge of IGBTs. The IGBTs used in this power supply were rated at 3.3kV and 1.2kA. The boost transformers utilized an amorphous nano-crystalline iron core operated at 20kHz with a bidirectional magnetic field swing of 1.6 Tesla. A parallel LC resonator was used on the secondary winding to achieve a high boost ratio. The transformers were measured to have 320W of loss per core during full power operation. The loosely coupled resonant secondary allows a boost ratio of 60:1 while using a turns ratio of 19:1 [4]. The turns ratio of the transformer is chosen to provide the required leakage inductance on the secondary to achieve a 20kHz resonant frequency with the parallel resonant capacitors.

The transformer cores were developed by National Arnold Magnetics and are constructed of 0.0008" nano-crystalline laminates for low loss at high frequency operation while maintaining a high magnetic permeability. The characteristics of the core material are presented in Table 1-1.

Table 1-1 Nano Material Characteristics [4]

| Mu                    | 50,000       |

|-----------------------|--------------|

| Lamination Thickness  | .0008"       |

| Lamination Insulation | 1 μM Namlite |

| Stacking Factor       | ~90%         |

| Bsat                  | 12.3 kG      |

| Core Loss (our use)   | ~300 W       |

| Core Weight (our use) | ~95 lbs      |

| Power (each core)     | 330 kW       |

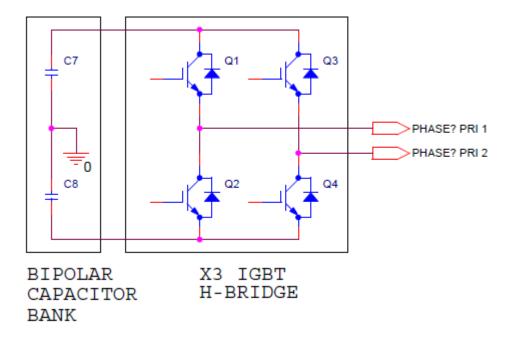

The IGBT network consists of a set of 12 IGBTs configured in a set of three independent full h-bridges, with the top of each bridge connecting to the positive capacitor bank at +1250V and the bottom connecting to the negative capacitor bank at -1250V as shown in Figure 1.2.

Figure 1.2 Bipolar bank and IGBT h-bridge

The IGBTs are mounted on a low inductance buss plate with a rail to rail inductance of 4nH, allowing snubberless operation of the IGBTs by preventing overvoltage conditions generated by high frequency ringing during switching events, where dI/dt can exceed 10kA/uS [5]. Total inductance of the input DC link is further reduced by using low ESL stiffening capacitors mounted directly to the IGBT bus plates providing a total input inductance on the order of 7nH [6].

The power supply uses zero voltage switching to reduce switching losses, where primary winding current is carried by the IGBTs freewheeling diode during the switching event. The

output voltage of the supply is controlled by PWM of the duty cycle of the switching period between 2.5us and 55us per half cycle which provides approximately 10% control range on the voltage output which is sufficient to stabilize output voltage during capacitor bank droop. PWM period is controlled by an adaptive feed forward / feedback system which provides very low ripple on the order of 150V. The voltage waveform on the transformer primary is shown in Figure 1.3.

Figure 1.3 Transformer primary waveform [4].

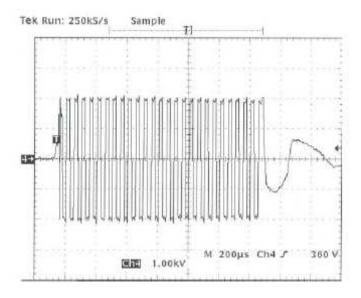

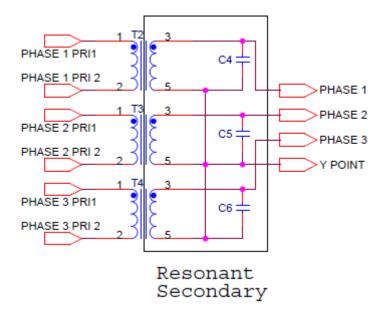

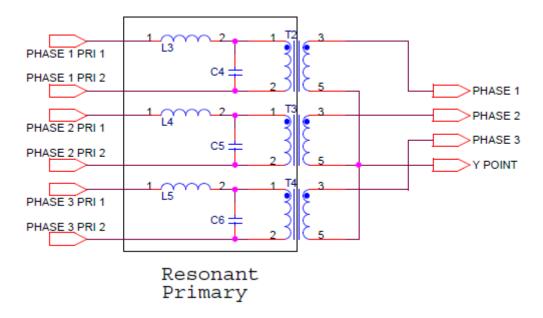

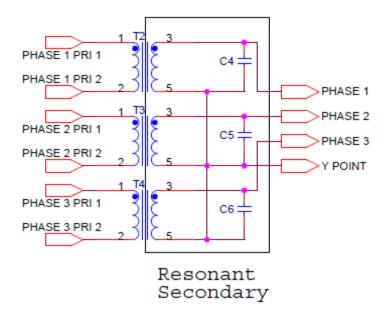

The secondaries of the transformers are connected in a Y configuration, each transformer with a parallel resonant capacitor as shown in Figure 1.4.

Figure 1.4 Three phase resonant transformer system.

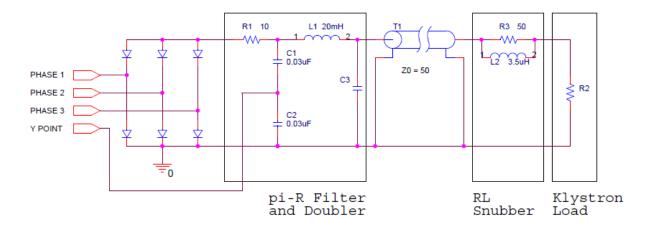

The three output phases are connected to a three phase rectifier feeding a center tapped capacitor bank with the center tap connected to the Y point on the transformer secondaries as seen in Figure 1.5. The rectifier consisted of a string of 1.4kV, 75A diodes with a 50ns reverse recovery time [7].

Figure 1.5 Rectifier, doubler, filter and RL snubber.

A resistor is placed in series, forming part of a pi-R filter, along with a series inductor and shunt capacitor after the center tapped doubling capacitor. The power supply is connected to the klystron load through a coaxial transmission line and a series RL snubber.

Testing of a crowbar system demonstrated de-Qing of the resonant transformers, automatically interrupting power transfer to the klystron tube. In the event that modulation on the transformer primary continued, only a slight increase in total energy dissipated into the klystron, on the order of 10J, was observed.

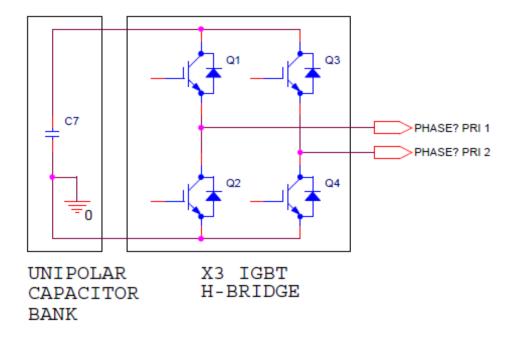

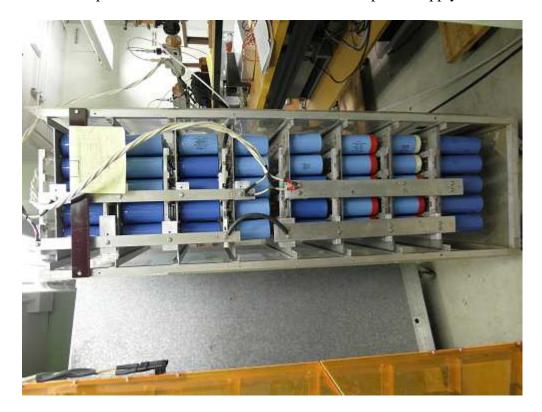

Other resonant transformer topologies have been explored for high voltage, high power modulators [8]. A long pulse modulator capable of producing a 25kV, 10A pulse of 1-2ms has been developed at E2V technologies. In this system, a unipolar electrolytic capacitor bank powers three independent full h-bridges that drive a resonant LC tank circuit connected across the primaries of three ferrite core transformers. The secondaries of the transformers are connected in a Y topology with the center tap floating. The output of the transformers is then rectified with a three phase rectifier and connected to an LC low pass filter to reduce harmonics and ripple.

In this particular power supply, the input DC link is powered of a unipolar capacitor bank charged from a three phase IGBT PWM rectifier designed to maintain the capacitor bank in a suitable voltage range while drawing power from the AC mains at unity power factor to comply with harmonic and flicker regulations. The size of the capacitor bank is minimized by utilizing intelligent charging methods and designing the power converter with a suitable dynamic boost range to compensate for increased voltage droop during each output pulse. With the bank used in this power supply, a voltage droop of 25% is expected during each

pulse. The capacitor bank is comprised out of electrolytic capacitors connected to a low inductance bus plate in a unipolar configuration, and powering three independent h-bridges as shown in Figure 1.6.

Figure 1.6 Unipolar bank and IGBT h-bridge

Each h-bridge drives a resonant boost transformer, configured with a resonant LC tank circuit on the primary as shown in Figure 1.7 with each transformer primary in parallel with the capacitor in the tank circuit. The transformer is constructed out of ferrite I-bars and has single layer primary and secondary windings. The cores are magnetically independent.

Figure 1.7 Resonant primary tank circuit

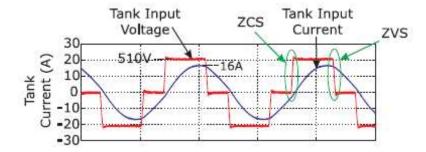

The transformer secondaries are connected in a Y topology, with the Y point floating, and are connected to a three phase rectifier. Output voltage is controlled by adjusting both the phase between the primary voltage and current as well as the duty cycle of the input waveform. In order to minimize switching losses, soft switching is obtained by using ZCS during IGBT turn on and ZVS during IGBT turn off. ZCS at the leading edge is ensured by phase shifting the drive waveform so the IGBT turns on during current zero cross, while output voltage control is established by PWM of the width of the pulse. Input dc link capacitor bank voltage is adjusted so that the lagging edge of the IGBT pulse occurs when the primary current is being commuted by the antiparallel diode and zero switching occurs as shown in Figure 1.8.

Figure 1.8 IGBT current and tank voltage[9].

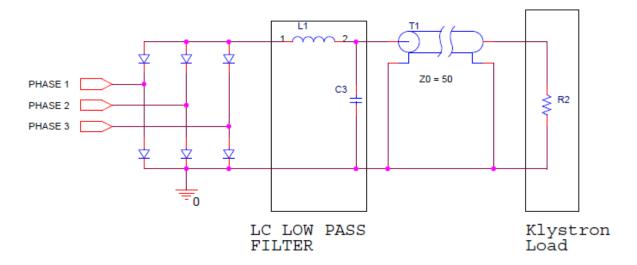

The output of the rectifier feeds an LC lowpass filter as shown in Figure 1.9 that acts both to reduce harmonic noise and ripple but also as the output DC link storage capacitor. The klystron load is connected to the supply by a coaxial transmission line.

Figure 1.9 Output LC filter.

Research at E2V technologies has shown that klystron cathode damage can occur if deposited energy during an arc exceeds approximately 20J [9]. A crowbar circuit has been connected across the power supply output to shunt stored energy in the LC filter's capacitor in the event of a tube arc. An unfortunate side effect of using an LC filter is that the filter's capacitor is directly connected in parallel across the klystron tube with minimal series

inductance between the capacitor and the load, thereby increasing the fraction of energy that can be dissipated into the tube before the crowbar circuit fires.

## 1.4 Harmonic Mitigation

Reduction of switching noise and ripple in the output waveform is an important consideration when driving klystron tubes, since the tube's gain is a function of input voltage and current: such fluctuations in input voltage will result in fluctuation in RF gain generating a noisy output. Several methods of harmonic mitigation may be implemented to reduce noise and output ripple in an SMPS. The main source of harmonic noise in a three phase SMPS is the 6<sup>th</sup> harmonic of the switching frequency, generated by the three phase full wave rectifier. Elimination of the 6<sup>th</sup> harmonic will greatly reduce output voltage ripple. Further it is important to insure that the amplitudes of the secondary voltages are equal of the system will produce 1<sup>st</sup> and 2<sup>nd</sup> harmonic ripple as well [4].

The most basic methods of reducing ripple involves increasing parallel capacitance on the output DC link, however this introduces many undesirable characteristics to a SMPS driving a klystron that requires rapid output pulses. The increased capacitance provides more stored energy on the output bus that may damage the klystron in the event of an output arc [9]. Further the increased capacitance increases the rise and fall time of the pulse, wasting power and generating unnecessary heating of the klystron collector.

Another basic form of ripple control is an LC low pass filter [8]. Such filters rapidly reduce harmonic noise above their cutoff frequency, however to provide sufficient ripple reduction, the size of the parallel capacitor would increase rise time or may damage a klystron tube in the event of an internal arc, thereby requiring the use of an output crowbar circuit.

A shunt LC harmonic filter may be connected across the output and tuned to selectively filter the 6<sup>th</sup> harmonic, however this filter losses effectiveness away from its resonant frequency, potently increasing noise if frequency is varies to stabilize output voltage. If the input capacitor bank is sufficient large, the switching frequency range may be placed near to the filter resonance at all times allowing the filter to reduce 6<sup>th</sup> harmonic noise effectively.

Reduction in harmonics and ripples was obtained by utilizing a pi-R filter in the output, constructed by placing a 6 ohm resistor in series with the output of the rectifier stack and an LC pi filter on the output. Pi-R filters have been shown to greatly reduce output ripple while allowing fast rise times [3]. An additional benefit of pi-R filters is the ability to limit dI/dt during an output arc [7] thereby protecting the klystron from damage and increasing the probability that the fault will self-clear before the resonator is de-Qed.

#### 1.5 Summary

Techniques for designing high voltage, high power resonant SMPS have been presented in this chapter. The first section presented several designs of high power SMPS, and high voltage SMPS topologies. It was generally concluded most high voltage high power systems utilize either closely coupled transformers operating at 60Hz or loosely coupled resonant transformers with nano-crystalline cores operating at frequencies around 20kHz. The higher operating frequency allows a considerably smaller power conversion system that operates at higher efficiencies due to reduced core losses. The utilization of a resonant transformer system allows a boost ratio higher than the turns ratio, and the capability to utilize soft switching to greatly reduce switching losses.

The second section presented designs and characteristics of loosely coupled transformers, different varieties of primary and secondary compensation, and methods of increasing power transfer.

The third section covers an in depth review of resonant SMPS power converters, including a designs of three phase resonant converters built at Los Alamos National Lab and E2V technologies, and results of their testing.

The fourth section presented techniques of harmonic mitigation, their benefits and drawbacks. It was concluded that increasing parallel output capacitance is not a feasible option due to the decreased rise time and potential to damage attached klystron loads in the event of an arc fault. Ideal candidates for harmonic reduction include pi-R filters and LC harmonic filters due to their low energy storage.

# Chapter 2 Power Supply Design Overview

This chapter presents an overview of the design requirements and components available to construct the power supply presented herein. The first section presents the requirements and design constraints for construction of the power supply. Requirements on the power supply include output voltage and current capabilities, fault tolerance, output voltage range, output stability, pulse duration, serviceability, safety, tolerance for voltage droop on the capacitor bank, and external control of parameters. Design constraints include the use of certain transformer cores, IGBTs, rectifier diode stacks, and capacitor banks which were either donated to the project or were available as surplus. The second section presents a summary of the chosen design and the reasons certain features were selected.

# 2.1 Design Requirements and Constraints

The power supply presented in this thesis is designed to power a klystron amplifier for a fusion power research experiment. The klystron in question requires a cathode potential of -75kV and draws 40A of current, yielding a nominal impedance of 1875ohms. The klystron presents to a good approximation, a constant, purely resistive load with current linear to voltage within the rated operating range. Due to space constraints within the experimental area the power supply is required to have a compact design and be located approximately 30ft from the klystron tube which it powers. For safety the power supply and associated capacitor banks must be located in a caged area within the experimental area; however the system's output must be variable necessitating remote control over a computer terminal. To be placed into the requisite location in the engineering bay, the power supply must be lifted into position using a ceiling crane, favoring a light weight, modular design.

Due to the presence of high strength pulsed magnetic fields in the area, the power supply must not generate any ground loops when electrically connected to the experiment, requiring that all connections maintain galvanic isolation. Due to this requirement, all i/o lines connecting the power supply to the control system must be fiber optic, the secondary side of the power supply must get its ground from the klystron tube, and all voltage and current sensors must be galvanically isolated from the control system.

The klystron tube being powered is designed for sub-millisecond pulses, however for this experiment; the tube will be required to produce a 10ms pulse, in excess of its design specifications. Although this is permissible when using short duty cycles, it is probable that

the tube will occasionally arc internally. The stored energy in the power supply secondary must be sufficiently small so that no damage will occur to the tube. Further the power supply must be able to tolerate an arc fault that reflects a high voltage pulse back up the transmission line without damage. As the klystron gain is sensitive to voltage fluctuations, output ripple and harmonics must be minimized.

Due to budget constraints, a number of pats on the power supply were recycled from previous experiments, or donated to the project by LANL. The main capacitor bank is comprised of 450V electrolytic capacitors, each with capacitances of 1.8mF, 2mF or 2.4mF restricting the bank voltages to multiples of 450V. The capacitors were mounted in racks, with each rack containing 8 trays, with each tray containing 35 electrolytic capacitors. The bank has a total capacitance of 0.3F when configured in a 900V arraignment. Due to the configuration of the bus bars connecting the trays, it is easiest to configure the bank in the 900V configuration. A hipotronics high voltage power supply was obtained to charge the dc link input capacitor bank, capable of charging the bank to 900V.

A set of 20 matching Mitsubishi CM1200HB-66H IGBTs was donated, each rated at 3.3kV and 1.2kA with a rated pulse current of 2.4kA [A], of these 12 are used to construct a set of 3 full h-bridges. In addition, a number of 50kV 0.05uF Mylar foil capacitors, four low ESL IGBT bypass capacitors rated at 4kV, 10uF and 10nH ESL, three nano-crystalline iron cores with a length and width of 9.5" by 14" with a cross section of 2.5" by 1.75", and a three phase full wave rectifier assembly were also donated.

# 2.2 Summary

This chapter presented the available parts, requirements, and constraints on the power supply described herein. These components and requirements formed the basis of the power supply design and governed the physical layout, dimensions and electrical parameters chosen. An electrolytic capacitor bank powered three phase resonant topology with independently driven primaries and Y connected parallel resonant secondaries was chosen. The secondaries are connected to a doubling three phase rectifier, with a pi and 6<sup>th</sup> harmonic shunt LC filters to reduce output ripple. The klystron load is connected to the power supply through RG-8/U coaxial cable and has an LR snubber in series and a triggerable spark gap snubber in parallel. The system is controlled with a fiber optically coupled microcontroller with galvanically isolated analog inputs for feedback control and fiber optic communication to the control computer.

# Chapter 3 Power Supply Design

This chapter presents the design of the resonant power supply including power electronics, magnetics, filtering, crowbar and snubber. The first section presents an overview and block diagram of the power supply hardware. The second section presents the connection and control of the capacitor charging power supply. The third section presents the design and construction of a smaller short pulse capacitor bank for safely testing the power supply and conditioning the klystron tube. The fourth section describes the design and construction of the long pulse capacitor bank including the electrolytic capacitors, capacitor fuses and connection to the bus plates, and the interconnection to the power supply. The fifth section presents the design of the IGBT switching network, its topology, the connection from the capacitor bank, the low ESL stiffening capacitors, a low inductance switching relay designed to disconnect the capacitor bank from the IGBT network, the low inductance bus plates and their insulation, the IGBTs and their gate drivers, and the connection to the resonant transformer primaries. The sixth section provide an overview of the transformer design, its nano-crystalline iron core, the design of its windings, the enclosure and insulation of its secondary winding within dedicated oil tanks, the feedthrough and cable connections to the transformers, the connection of the parallel resonant capacitors, and testing of the transformer's transfer function. The seventh section presents an overview of the doubling three phase rectifier configuration. The eight section presents filter networks for harmonic mitigation. The ninth section presents safety systems to protect the klystron load including an LR snubber and crowbar spark gap. The tenth section summarizes the chapter.

### 3.1 Overview and Block Diagram

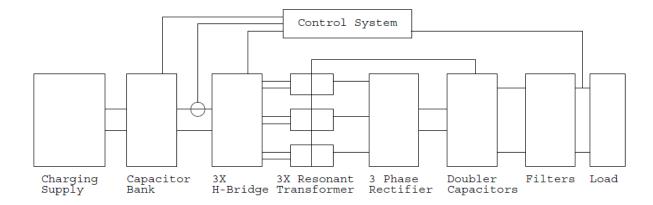

The power supply is arraigned in an easily serviceable, modular design, consisting of a charging supply, a capacitor bank, three h-bridges, three resonant transformers, a doubling three phase rectifier, an output filter and a control system as shown in Figure 3.1.

Figure 3.1 Power Supply Block Diagram.

The capacitor bank charging supply charges the capacitor bank to 900V between pulses, ensuring acceptable voltage bounds during the pulse. The input DC link capacitor bank is mounted in three racks, configured as a 900V, 0.3F bank with each electrolytic capacitor connecting to the bank's bus plates using a stainless wire fuse that will open in the event of an internal short. The bank connects to the power supply using twisted pair wires which plug into the low inductance bus plates holding the IGBTs. The bus plate is connected directly to the low ESL capacitors, providing the IGBTs a stiff DC voltage source on the poles of the h-bridges. The bus plate holds three full h-bridges, each driving the primary of a resonant transformer. The primaries of the transformers are electrically independent and the cores are magnetically independent. The secondaries are designed with high leakage inductance, a

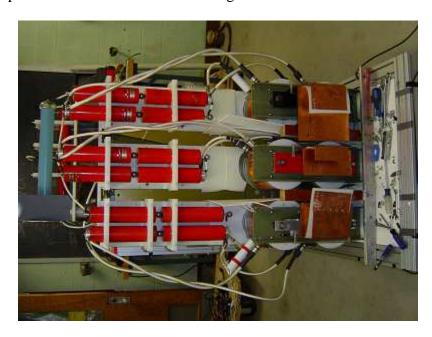

parallel resonator capacitor and are connected in a Y topology to a doubling three phase rectifier. The output of the supply is optionally filtered by a pi and harmonic filter to reduce ripple and harmonic noise. The klystron load is connected to the supply by a 20-30ft long RG-8U coaxial cable. An RL snubber is placed in series with the klystron to protect the tube in the event of an internal arc and prevent HV transients from being reflected down the transmission line. A triggerable spark gap is placed in parallel with the klystron to crowbar the output in the event of an internal arc. The power supply is controlled by a microcontroller based control system that varies switching frequency to stabilize voltage output. The microcontroller varies switching frequency as a function of capacitor bank and output voltage. A picture of the power supply is presented in Figure 3.2.

Figure 3.2 Resonant power supply in construction.

# 3.2 Capacitor Charging Power Supply

The capacitor bank charging supply charges the capacitor bank to 900V between pulses, which will be taken at very low duty cycle; one 10ms pulse approximately every 2-4 minutes. Due to the low duty cycle, the charge rate may be very slow, and the use of a linear power supply using hysteresis control is acceptable. A hipotronics 805-1A power supply as shown in Figure 3.3 capable of 1A output in the kV range will be used to charge the capacitor bank.

Figure 3.3 Hipotronics power supply.

The power supply is capable of being run directly from the AC mains and contains an internal control system to regulate output voltage. The power supply features operation off of

a 208/230VAC three phase input, 10% regulation and under 5% ripple [B]. Given that the power supply's voltage rating exceeds the voltage required on the bank, and the supply has current limiting, constant current charging may be utilized. The time to charge the capacitor bank is given by (3.1).

$$T = \frac{CV}{I} \tag{3.1}$$

For a 900V, 0.3F capacitor bank and 1A charging current, the power supply will be able to charge the bank from 0V to full voltage within 270s or 4.5 minutes. During cycling, the voltage droop on the bank will be a small fraction of the bank voltage allowing faster charge times between shots.

# 3.3 Testing Capacitor Bank

In order to safely test the power supply during development, it was necessary to construct a smaller, lower capacitor bank to minimize stored energy. A testing bank consisting of 24 450V, 6.2mF capacitors configured into a 900V, 37mF bank as shown in Figure 3.4.

Figure 3.4 Testing capacitor bank.

The bank is charged by an internal rectified microwave oven transformer, with bank voltage being controlled by a hysteresis controller. The controller uses a comparator circuit to turn on the microwave oven transformer if bank voltage is below the preset voltage value. The system is designed to have 10V hysteresis.

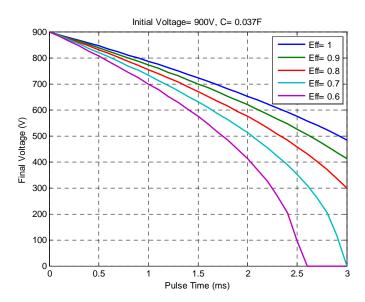

The capacitors are interconnected with copper bus bars and the bank is connected to the power supply with four 10 gauge wires twisted together to reduce inductance. The voltage droop on the capacitor bank may be solved for from the dissipated pulse energy, stored bank energy and power supply efficiency as seen in equation (3.2).

$$V_{f} = V_{i} \sqrt{1 - \frac{E_{pulse}}{\eta E_{bank,i}}} = V_{i} \sqrt{1 - \frac{V_{out}I_{out}T_{pulse}}{\eta (1/2)CV_{i}^{2}}}$$

(3.2)

Assuming output voltage and current are constant due to feedback control, and that the rise time is negligible, the voltage droop on the capacitor bank can be plotted vs pulse time, as shown in Figure 3.5. See matlab code in [G];

Figure 3.5 Testing bank voltage droop.

## 3.4 Long Pulse Capacitor Bank

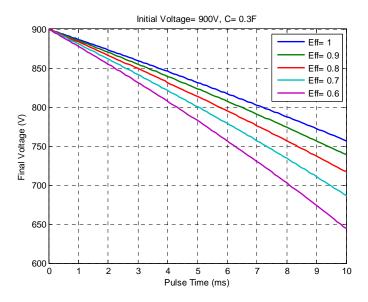

An increased capacitance will be required to extend the pulse duration to 10ms and beyond in order to reduce the voltage droop during the pulse to acceptable levels. The main capacitor bank consists of 450V electrolytic capacitors, each with capacitances of 1.8mF, 2mF or 2.4mF. The capacitors are mounted in racks, with each rack containing 8 trays, with each tray containing 35 electrolytic capacitors. The bank has a total capacitance of 0.3F when configured in a 900V arraignment. Each tray is connected to a set of bus bars on the back of the rack, and each capacitor is connected to the trays through a stainless wire fuse to prevent the bank charge from being shunted through a single capacitor in the event of an internal short. Assuming output voltage and current are constant due to feedback control, and that the rise time is negligible, the voltage droop on the capacitor bank can be plotted vs pulse time, as shown in Figure 3.6.

Figure 3.6 Main bank voltage droop.

#### 3.4.1 Electrolytic Capacitors

The main capacitor bank consists of 450V electrolytic capacitors, each with capacitance of 1.8mF, 2mF or 2.4mF as shown in Figure 3.7. These capacitors were arraigned into trays of 35 capacitors in three racks, with two racks containing all capacitors connected in parallel and the third rack containing two electrically separate banks. During construction it was ensured that each of the two larger banks and the two smaller banks has equal capacitance. The two half rack banks are placed in parallel with the two full rack banks, and then placed in series with each other forming a 900V 0.3F capacitor bank.

Figure 3.7 Main bank capacitors.

# 3.4.2 Capacitor Fuses

Due to the possibility of a capacitor failure and the parallel connection of the capacitors in the bank it is necessary to individually fuse each capacitor such that in the event of a

capacitor developing an internal short, the energy of the entire bank is not shunted through the failed capacitor.

Each capacitor is connected to an aluminum tray with one terminal and a bus bar above the tray through the wire fuse. The capacitor fuses consist of a stainless connecting wire between each capacitor and the bus bars on each tray that will melt open in the event of an internal short, as shown in Figure 3.8.

Figure 3.8 Capacitor bank fuses.

#### 3.4.3 Capacitor Bank Bus Plates

Each capacitor tray is connected to a set of vertical bus bars in the rear of the rack as shown in Figure 3.9 allowing the trays to be electrically connected in parallel. One bus bar is connected to the base of the aluminum trays, while the other vertical bus bar connects to the

bus bars on each tray. Each bus bar is connected to low gauge interconnect cable that connects the capacitor bank racks to each other and to the power supply.

Figure 3.9 Capacitor bank bus bars.

# **3.4.4** Capacitor Bank Interconnect Cables

The capacitor banks are connected to the power supply's low inductance buss plate over a set of four twisted wires in order to minimize inductance while allowing flexibility in the location of the banks with respect to the power supply. The effects of any inductance contributed by the interconnect cables are minimized by the DC link stiffening capacitors on the power supply.

# 3.5 Switching Network Design

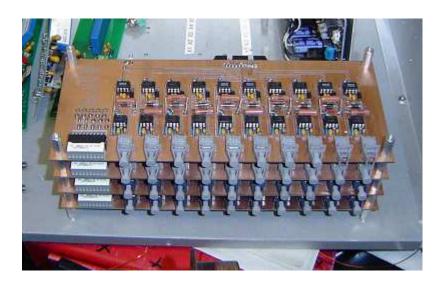

The switching network for this power supply consists of 12 Mitsubishi CM1200HB-66H IGBTs arraigned in three independent h-bridges, each riving the primary of a resonant transformer. The use of a low inductance bus plate to mount the IGBTs and the use of low ESL DC link stiffening capacitors allows snubberless operation near the transformer's resonant frequency

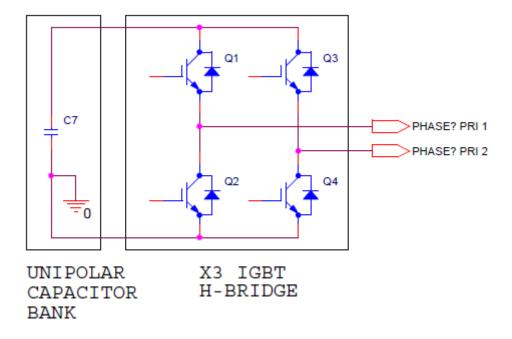

#### 3.5.1 Topology

The IGBTs on the bus plate are arraigned in a full h-bridge configuration with each transformer being independently driven as shown in Figure 3.10.

Figure 3.10 H-Bridge Topology.

Each IGBT has an antiparallel diode capable of commuting current during zero voltage switching during certain operating modes. Due to the low inductance of the bus plates that the IGBTs are mounted on and the presence of the DC link stiffening capacitors, snubberless operation is possible without ringing or high voltage spikes during switching events.

#### 3.5.2 Cable Interconnects From Capacitor Bank

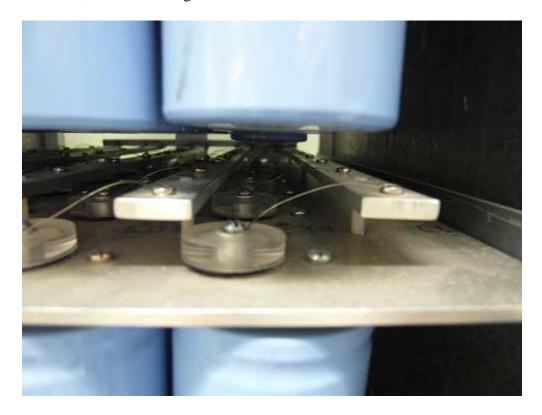

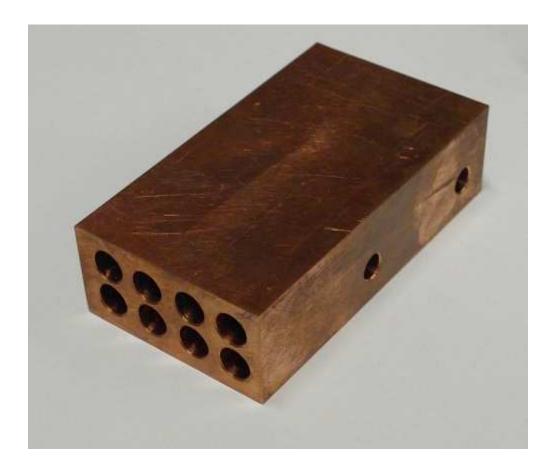

Copper blocks located at the terminals of the low inductance bus plate allow connection of the capacitor bank cables to the power supply as shown in Figure 3.11.

Figure 3.11 Capacitor bank interconnects.

The copper blocks have holes drilled to match the oversized banana plugs on the end of the cables. The testing bank connects with two wires per terminal while the main bank connects with eight as shown in Figure 3.12.

Figure 3.12 Main capacitor bank interconnect block.

# 3.5.3 Low ESL Stiffening Capacitor Bank

Transition between the higher inductance electrolytic capacitor bank and the low inductance buss plates on the power supply requires the use of low ESL stiffening capacitors on the input DC link. A set of four General Atomics 37547 low ESL capacitors rated at 4kVDC, 10uF, and 10nH previously used at LANL were used as bypass capacitors [10]. The capacitors are each rated to handle high transient currents of up to 4kA, and high rms currents of 100+ amps. The capacitors are connected directly to the ends of the low inductance buss plates. In addition, a small 900V, 2mF capacitor bank is added to the buss plates to further increase capacitance as shown in Figure 3.13

Figure 3.13 IGBT bypass capacitor connection.

### 3.5.4 Low Inductance Relay

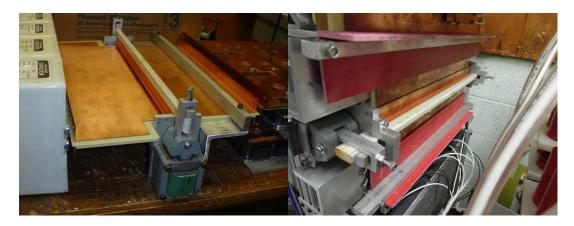

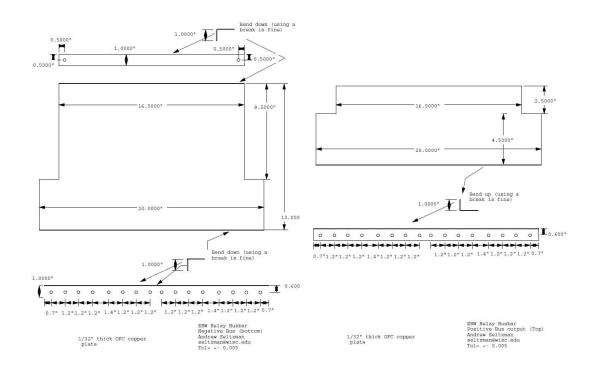

A low inductance relay has been designed to serve as a master connect/disconnect switch capable of carrying the full current while maintaining a low inductance current path. The relay consists of a pair of 16.5" wide bus plates separated by a 1/16" of insulating G10-FR4 fiberglass. The top bus plate consists of a split input and output segment that can be connected and disconnected by physically pulling the overlapping segments of the busbar together as shown in Figure 3.14.

Figure 3.14 Low inductance relay.

The output busbar is rolled into a curved shape, so that with no pressure on it, it will disconnect from the input busbar. A pair of high strength mechanical AC relays connects the circuit by pulling a fiberglass bar against the top bus plate. The fiberglass bar is machined into a curved shape along its length and jacketed with a silicone boot to compensating for any deflection under stress and providing equal pressure to the busbar along its contact area. In this design the input and output busbars overlap by approximately 0.75" allowing the relay to carry the full power supply current. Dimensions of the relay busbar plates are given in [D].

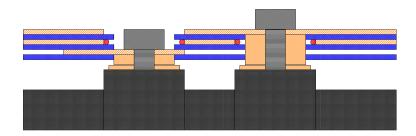

#### 3.5.5 Low Inductance IGBT Busbars

A voltage stiff source must be provided across the terminals of the IGBTs requiring a low inductance DC link. The IGBT busbars are designed to provide the minimum possible inductance, while allowing high current capability, physical rigidity, capability to connect to both the transformer primaries and low inductance relay with minimal added inductance and a large safety margin on insulation voltage standoff. Dimensions of the busbar plates are given in [E].

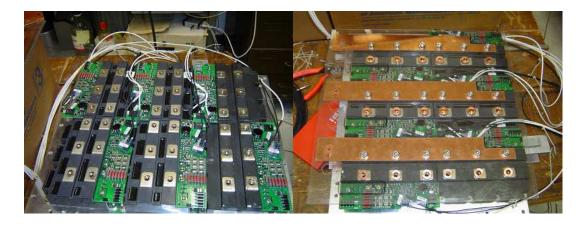

The IGBTs are arraigned into two modules, with each module containing three half h-bridges. Each module consists of an aluminum plate onto which the six IGBTs are attached. The IGBT gate drives connect directly to the IGBT modules and the associated wiring is shielded from the input and output busbars with a 1/16" polycarbonate sheet. A set of 0.75" OD, 0.375" ID copper standoffs connect to the output terminals of the IGBTs through the polycarbonate insulating plates and connect to the output busbars which are then bolted down

to the IGBT modules as shown in Figure 3.15. All busbar components are made out ov 1/16" thick oxygen free copper (OFC).

Figure 3.15 IGBT output busbars.

A second layer of 1/16" polycarbonate insulation is placed on top of the output busbars followed by the positive input busbar, which connects to the IGBTs with copper standoffs, followed by a third layer of polycarbonate insulation and the negative busbar as shown in Figure 3.16.

Figure 3.16 Input busbars.

Additional insulation between the busbars is accomplished by placing silicone o-rings between the layers of polycarbonate insulation so that when the busbars are tightened down,

the o-ring is compressed between the insulation layers forming an air tight seal. Additionally, overhang of the insulation layers increases the path between conductors, thereby reducing the possibility of arc tracking as shown in Figure 3.17.

Figure 3.17 Busbar layer cross section.

The two IGBT modules bolt together face to face with the positive busbars connecting with flanges near the output busbar terminals and the negative busbars connecting near the low inductance relay. The two output busbars for a given transformer are now located very close together, allowing a low inductance connection. The completed IGBT module bolts to the low inductance relay with flanged connections, allowing a low inductance connection. The insulation layers of the relay and IGBT module overlay by 0.25" preventing arc tracking at the flange connection as shown in Figure 3.18. All flange connections use pre-stressed aluminum compression bars to provide uniform force across the flange.

Figure 3.18 IGBT module connection flanges.

#### 3.5.6 IGBTs and Gate Drivers

The IGBTs used to assemble the h-bridges are Mitsubishi CM1200HB-66H modules rated at 3.3kV, 1.2kA continuous current 2.4kA pulsed current as shown in Figure 3.19. Testing at LANL has shown that these IGBTs can exceed the pulsed current rating for short duty cycle pulses used in these resonant power supplies when soft switching is used to limit junction power dissipation.

Figure 3.19 Mitsubishi CM1200HB-66H.

The IGBT gate drive signal was provided by a set of 1SD536F2-CM1200HB-66H gate drive modules manufactured by CT concepts. These gate drivers are matched to the electrical

requirements of the IGBT and offer a plug and play solution. Each module can provide +-36A of gate drive current and had 6kV isolation between any IGBT terminal and the DC power connection. Further, control and feedback of these modules is accomplished with a fiber optic interface, allowing galvanic isolation and immunity to electrical noise. The drivers allow the IGBT to achieve 15ns rise time and 20ns fall time. Full specifications are given in [F].

#### **3.5.7 Transformer Connections**

A set of intermediate busses connect the IGBT inverter module to the resonant transformers. The transformer bus connections are insulated with a sheet of fiber coated Mylar "whitepaper", allowing for a low inductance path to be maintained as shown in Figure 3.20.

Figure 3.20 Transformer connections.

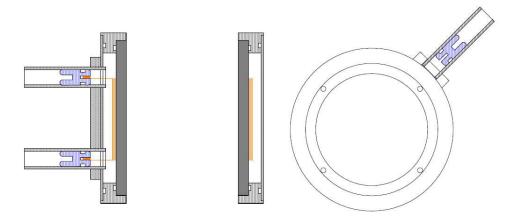

## 3.6 Transformer Design

A high power step up resonant transformer system has been designed for use on the power supply. The transformer is configured with electrically independent primaries and resonant secondaries connected in a Y configuration. Each secondary has a dedicated resonator capacitor connected in parallel across the winding as shown in Figure 3.21.

Figure 3.21 Resonant transformer configuration.

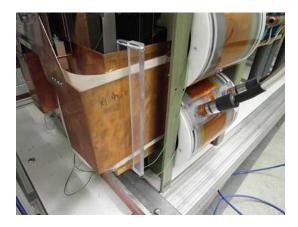

#### 3.6.1 Overview

The resonant transformer is designed to provide a sufficient secondary leakage inductance to use in a resonant circuit by designing a loosely coupled secondary winding. The transformer is based on a nano-crystalline iron core that has a large magnetic permeability, thereby providing sufficient volt seconds for high power transfer while allowing low loss at high frequency operation. A tightly wound 10 turn primary is connected

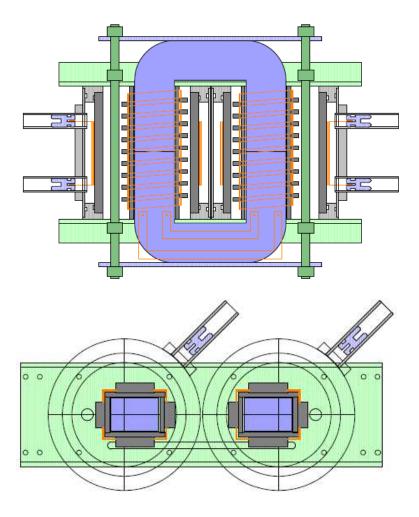

to the IGBT inverter while a loosely wound secondary has enough privatized magnetic flux to provide a sufficiently large leakage inductance. Each secondary winding is enclosed in a dedicated oil tank for insulation and corona suppression. The transformer is pictures in Figure 3.22 and its mechanical design is presented in Figure 3.23.

Figure 3.22 Resonant transformer.

Figure 3.23 Resonant transformer design.

# 3.6.2 Nano-crystalline Iron Core

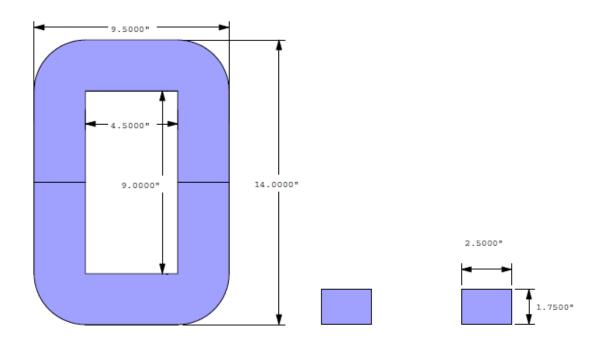

A set of three identical nano-crystalline iron cores were donated to the project by LANL. Each core has properties as given in Table 3-1 and dimensions as given in Figure 3.24. Testing determined that the cores saturate at 5.4E-3 Volt Seconds per turn full swing, sufficient for operation at 900V, 20kHz with a ten turn primary, requiring 4.5E-3 Volt Seconds per turn.

Table 3-1 Transformer Core Characteristics [4]

Mu 50,000

Lamination Thickness .0008"

Lamination Insulation 1  $\mu$ M Namlite

Stacking Factor ~90%

Bsat 12.3 kG

Current Saturation 5.4E-3 VoltSec/turn

Figure 3.24 Transformer core dimensions.

### 3.6.3 Primary Winding

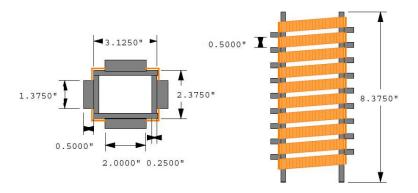

The transformer primary consists of a pair of 10 turn windings on each side of the core. Each winding used a 1/32" thick, 0.5" wide copper strap, wound in a helical manner around a 0.25" thick polycarbonate coil form. The primary is pictured in Figure 3.25 and has mechanical dimensions as given in Figure 3.26.

Figure 3.25 Transformer primary.

Figure 3.26 Transformer primary dimensions.

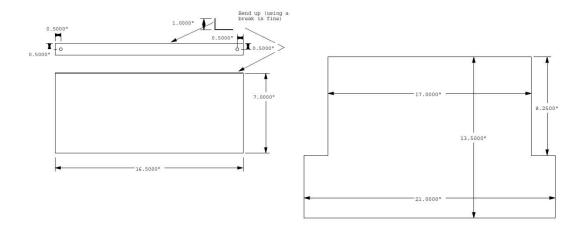

## 3.6.4 Secondary Winding Enclosure

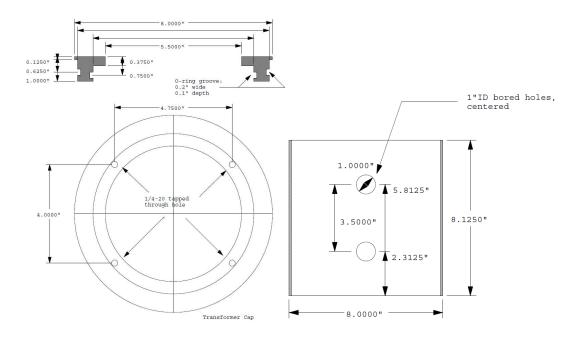

Due to the high frequency, high voltage operation, the secondary is susceptible to corona formation, potentially leading to arcing. To prevent this, each secondary in enclosed in a dedicated oil tank with dimensions as shown in Figure 3.27. The oil tanks may be evacuated during oil filling to prevent air bubbles from being trapped in the windings.

Figure 3.27 Oil tank dimensions

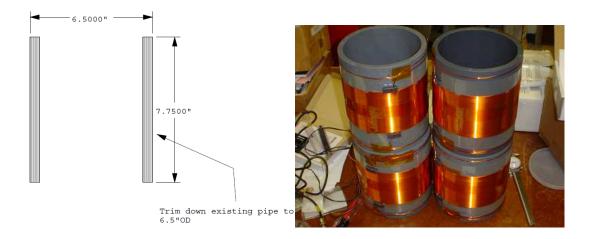

## 3.6.5 Secondary Winding

Each transformer has two loosely coupled secondaries, connected electrically in parallel. Each secondary winding is wound around a 6.5" diameter PVC coil form and consists of two layers of 22ga copper magnet wire connected electrically in parallel with a layer of Mylar foil insulation between them. Each secondary has 136 turns. The secondary winding dimensions and a picture are shown in Figure 3.28. The interior of the secondaries are lined with several axial lines of conductive copper tape which are then grounded to prevent capacitive coupling through the coil form from generating corona in the interior of the secondary oil tank.

Figure 3.28 Transformer secondaries.

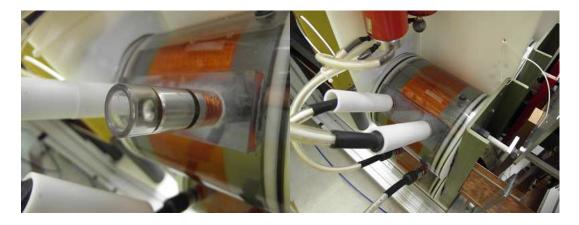

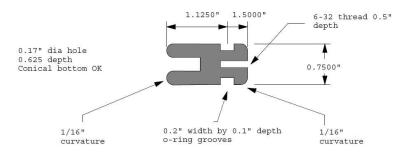

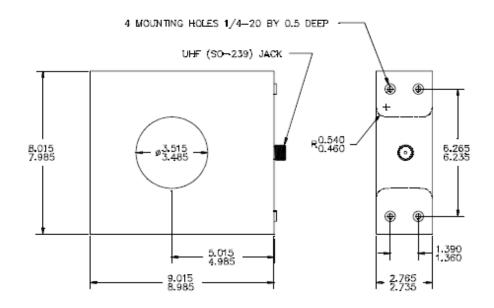

#### 3.6.6 Oil Tank Feedthroughs

A set of high voltage oil tank feedthroughs have been designed to connect the transformer secondaries to the resonator capacitor banks. The feedthroughs must provide adequate high voltage insulation between the two terminals, and other conductive objects in near proximity. The oil tank feedthroughs are shown in Figure 3.29 and a CAD of the assembly is shown in Figure 3.30.

Figure 3.29 Oil tank feedthroughs.

Figure 3.30 Assembled oil tank components.

Each feedthrough consists of a polycarbonate tube housing an aluminum plug as shown in Figure 3.31. The aluminum plug maintains an oil seal to the polycarbonate tube with an oring and has a 6-32 thread on the interior for attaching to the secondary winding and a banana plug socket for connecting to the associated cabling.

Figure 3.31 Aluminum plug.

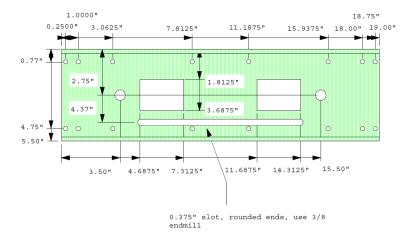

The polycarbonate tubes are physically supported by a polycarbonate block with a matching radius to the oil tank that allows the block to be glued to the surface as shown in Figure 3.32. All polycarbonate components are welded together using ethylene dichloride solvent.

Figure 3.32 Polycarbonate tubes and supports.

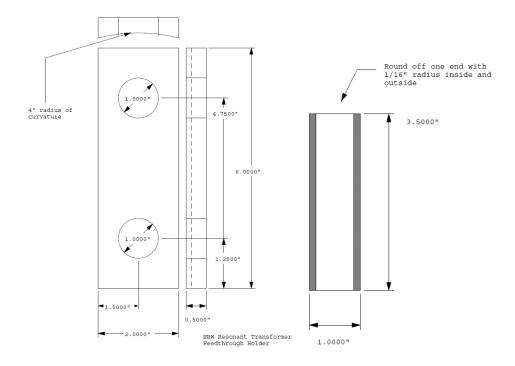

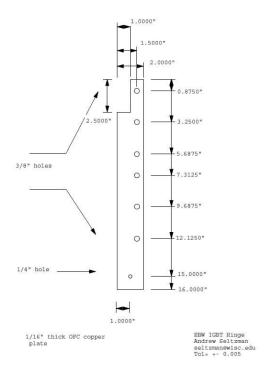

The transformers are assembled between a pair of fiberglass support plates which bolt to the secondary oil tanks and hold the cores in place. Dimensions for the support plate are given in Figure 3.33.

Figure 3.33 Transformer support plate.

# 3.6.7 Parallel Resonator Capacitor

The secondaries of each transformer are connected in parallel with a 0.05uF resonator capacitor assembly. Each assembly consists of four 50kV, 0.05uF Mylar foil capacitors connected in a series-parallel configuration to obtain a 100kV rating as shown in Figure 3.34. A set of rounded corona disks as shown in Figure 3.35 may be placed on the ends of the capacitors to reduce the risk of arcing.

Figure 3.34 Resonator capacitor assembly.

Figure 3.35 Corona disk.

#### 3.6.8 Variation of Frequency, Turns Ratio, and Load Resistance

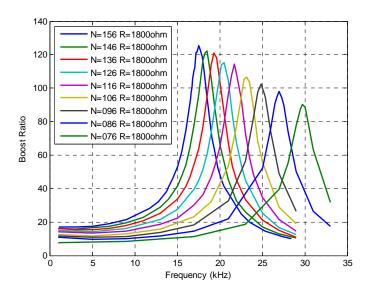

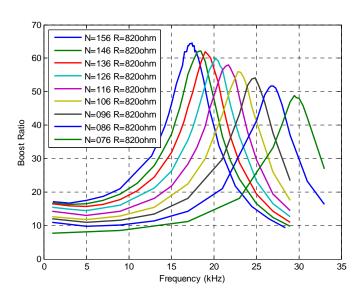

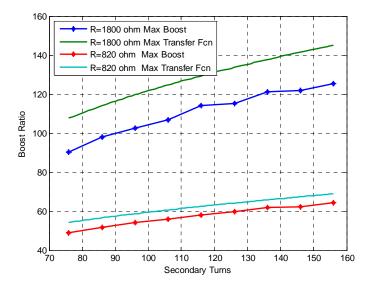

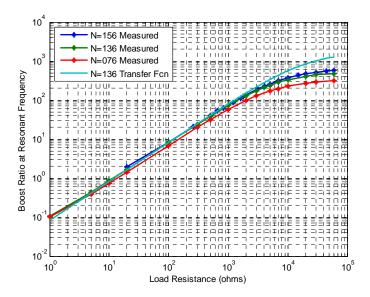

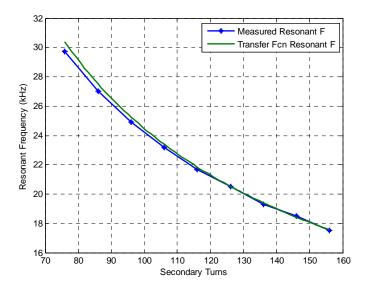

Several iterations of transformer secondaries were tested during the design process. Secondary turn numbers between 76 and 156 were tested between 1kHz and 30kHz with load resistances between 10hm and 60kohm. The frequency responses for transformers with a 1.8kohm load are presented in Figure 3.36, and frequency responses for transformers with a 820ohm load are presented in Figure 3.37. Far away from the resonant frequency, the boost ratio equals the turns ratio, while near resonance, the boost ratio is significantly higher than the turns ratio. Plots are generated with the matlab code found in [G].

Figure 3.36 1.8kohm frequency responses.

Figure 3.37 820ohm frequency responses.

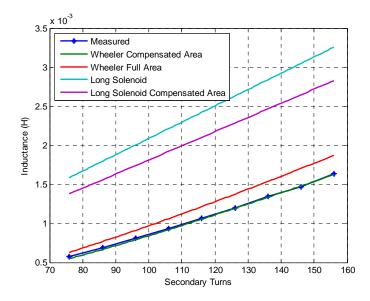

Several analytical models for leakage inductance of the secondary were compared to measurements from the transformer. These analytical models include the long solenoid approximation (3.3), the long solenoid approximation with area compensation (3.4) where

the area of the magnetic core is subtracted from the area of the secondary, making the approximation that magnetic flux is excluded from the core when measuring leakage inductance with a shorted primary. A second model for the inductance of a short solenoid was derived by wheeler in [11] and [12] is given by (3.5), with the corresponding area compensated version given by (3.6). The length of the coil, h, is given by (3.7) so that the inductance formulas may be evaluated in terms of N.

$$L_{long} = \frac{\mu_0 N^2 A}{h_{coil}} \tag{3.3}$$

$$L_{long} = \frac{\mu_0 N^2 \left( A - A_{core} \right)}{h_{coil}} \tag{3.4}$$

$$L_{wheeler} = \frac{10\mu_0 N^2 A}{\left(9r_{coil} + 10h_{coil}\right)}$$

(3.5)

$$L_{wheeler} = \frac{10\mu_0 N^2 \left(A - A_{core}\right)}{\left(9r_{coil} + 10h_{coil}\right)}$$

(3.6)

$$h_{coil} = N \cdot D_{wire} \tag{3.7}$$

The evaluation of these formulas is computed in matlab and plotted against measured values of inductance in Figure 3.38. The wheeler formula with area compensation is a nearly an exact match to the measured values of inductance. Note that in the matlab code, the formulas are multiplied by 0.5 since there is a parallel connection of the two separate secondary coils, thus halving the inductance.

Figure 3.38 Leakage inductance models.

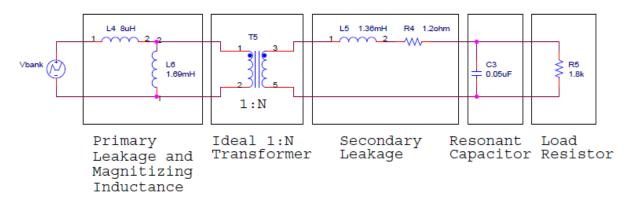

Analytical and numerical models for the transformer's transfer function were derived and compared to measured data. The final version of the transformer was chosen to have 136 turns, resulting in a primary leakage inductance of 8uH, primary magnetizing inductance of 1.69mH, secondary leakage inductance of 1.36mH, and a secondary series resistance of 1.2 ohms. A spice model of the transformer is presented in Figure 3.39.

Figure 3.39 Transformer model

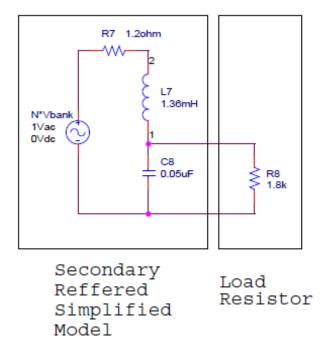

A simplified model of the transformer may be obtained by approximating that the magnetizing inductance is infinite, which remains valid as long as the transformers are run without saturating the cores, that primary resistance and leakage inductance is negligibly, and that the cores are magnetically lossless. The system may then be modeled as a resonant LC tank circuit driven by a voltage equal to the primary voltage times the turns ratio as shown in Figure 3.40. The spice simulation of this model is presented in Figure 3.41.

Figure 3.40 Simplified transformer model.

Figure 3.41 Spice simulation of simplified model.

The transfer function for the simplified model may be found analytically, with the total impedance seen by the voltage source given by (3.8) and the voltage gain given by (3.9).

$$Z(\omega) = \left[ R_{inductor} + j\omega L + \frac{\frac{R_{load}}{j\omega C}}{R_{load} + \frac{1}{j\omega C}} \right]$$

(3.8)

$$G(\omega) = \frac{V_{\text{sec}}}{V_{pri}} = \frac{N}{Z(\omega)} \left[ \frac{\frac{R_{load}}{j\omega C}}{R_{load} + \frac{1}{j\omega C}} \right]$$

(3.9)

$$G(\omega) = \frac{V_{\text{sec}}}{V_{pri}} = \frac{N}{\left[1 + \left(R_{inductor} + j\omega L\right)\left(\frac{1}{R_{load}} + j\omega C\right)\right]}$$

(3.10)

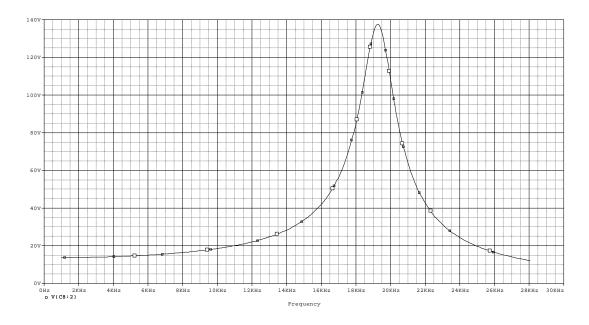

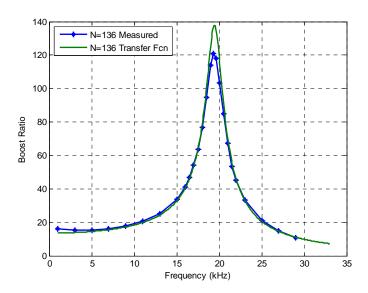

The plot of the transfer function closely matches the measured data as plotted in Figure 3.42 with the only difference being a slightly higher boost ratio at resonance which may be

attributed to the transfer function neglecting losses. This is further illustrated in a plot of the maximum boost ratio at resonance for a given turn number as shown in Figure 3.43 and the boost ratio at resonance for varying load resistance, as shown in Figure 3.44.

Figure 3.42 Comparison of transfer function and measured data.

Figure 3.43 Maximum boost ratio vs turns.

Figure 3.44 Boost ratio at resonance for varying load resistance.

The resonant frequency for the simplified system may be modeled analytically as (3.11). The analytical model matches the measured resonant frequencies with great accuracy as plotted in Figure 3.45.

$$F_{res} = \frac{1}{2\pi} \sqrt{\frac{1}{LC} + \frac{1}{(RC)^2}}$$

(3.11)

Figure 3.45 Measured and calculated resonant frequency.

The analytical models found for the loosely coupled transformer system accurately match measured values and numerical simulations and may be used to design the turns ratios of such systems in the future. Such models will greatly reduce the design time of such systems by allowing the elimination of trial and error approaches to loosely coupled resonant transformer design.

## 3.7 Doubling 3 Phase Rectifier